04 University of Plymouth Research Theses

01 Research Theses Main Collection

2015

# A Novel Power Conversion Approach for Single Phase Systems

#### AL-ZUBAIDI, SAIF THAMER FADHIL

http://hdl.handle.net/10026.1/3971

http://dx.doi.org/10.24382/4791 Plymouth University

All content in PEARL is protected by copyright law. Author manuscripts are made available in accordance with publisher policies. Please cite only the published version using the details provided on the item record or document. In the absence of an open licence (e.g. Creative Commons), permissions for further reuse of content should be sought from the publisher or author.

# A Novel Power Conversion Approach for Single Phase Systems

Saif AL-Zubaidi

#### Copyright ©2015 Saif AL-Zubaidi

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the author's prior consent.

#### This thesis is dedicated to

My mother, who sacrificed a lot for me and inspired me the meaning of sacrifice and success

The memory of my father, who taught me the truth of life

My wife, who is the source of happiness in my life and my companion to the

way of success

My children, who make my life full of beauty

To all people who I love

# RESEARCH DEGREES WITH PLYMOUTH UNIVERSITY

# A Novel Power Conversion Approach for Single Phase Systems

by

#### SAIF AL-ZUBAIDI

A thesis submitted to Plymouth University in partial fulfilment for the degree of

#### DOCTOR OF PHILOSOPHY

School of Computing and Mathematics

Faculty of Science and Technology

Plymouth University, UK

30<sup>th</sup> November, 2015

# Acknowledgements

First and foremost, I am grateful to Allah for his blessings and conciliation throughout my research work.

I would like to express my deepest appreciation to all those who helped and supported me in my research.

I would like to express my sincerest gratitude to my first supervisor Mohammed Zaki Ahmed, who gave me his care, full support, excellent guidance, patience, and encouragement. This work would not be possible without his guidance and persistent help.

My second supervisor, Paul Davey, thanks a lot for the valuable comments and useful discussions which helped me to present my work in a better way.

I am also grateful to the Iraqi Ministry of Higher Education and Scientific Research MOHESR and the Martyrs Establishment for the financial support.

I take this opportunity to express my gratitude to all members of the Electrical Engineering Department, College of Engineering, Al-Mustansiriya University for their help and support and specially Dr. Kassim, Dr. Isaam, Dr. Adheed, and Dr. Salah.

I would like to thank all Iraqi friends and colleagues at Plymouth University especially Salah, Bashar, Nadia for their support which made me I do not feel loneliness and alienation.

Finally, I would like to express my deepest love and appreciation to my family for their moral support. They were a source of inspiration for me. They gave me the strength and patience at all times.

Author's Declaration

At no time during the registration for the degree of Doctor of Philosophy has the author

been registered for any other university award without prior agreement of the Graduate

Sub-Committee.

Work submitted for this research degree at the Plymouth University has not formed part

of any other degree either at Plymouth University or at another establishment.

This study was financed by the Iraqi Ministry of Higher Education and Scientific Re-

search MOHESR and the Martyrs Establishment-Iraq.

A programme of advanced study was undertaken, which included the extensive reading

of literature relevant to the research project and attendance of international conferences

on power electronics.

The author has presented papers in the following international conferences:

1. IEEE IFEEC 2013, The First International Future Energy Electronics Conference,

Tainan, Taiwan, November 2013.

2. IEEE COMPEL 2014, The Fifteenth IEEE Workshop on Control and Modelling

for Power Electronics, Santander, Spain, June 2014.

3. IEEE PEDG 2015, The Sixth International Symposium on Power Electronics for

Distributed Generation Systems, Aachen, Germany, June 2015.

Word count of main body of thesis: 55307

ii

## A Novel Power Conversion Approach for Single Phase Systems

#### Saif AL-Zubaidi

#### Abstract

A novel single phase rectification technique with a new architecture and control scheme is proposed. The new rectifier consists of switched capacitor branch in parallel with the diode bridge rectifier. The switched capacitor branch includes a capacitor and a bidirectional switch arranged in series so the switch can control the charging and discharging of the capacitor. The control strategy is carefully designed to ensure the output voltage of the rectifier is above a chosen threshold level and to maintain high input power factor with reduced line current harmonics. Circuit configuration, design parameters, principles of operation and the mathematical analysis are presented. The new architecture provides a reduction in the size of the DC side capacitor. This reduction can be as low as less than 10% of the size of the typical smoothing capacitor in the conventional single phase rectifier. The proposed concept is verified by the experimental results over a range of case studies.

A novel buck-boost DC-DC converter architecture is also proposed. This converter utilises the close inversely-coupled inductors topology in both its conversion stages (buck and boost). The new converter aims to reduce the switching noise that usually accompanies the buck and boost circuits. This can be done by maintaining a continuous flow of current in both converter stages which results in a large reduction in the back e.m.f induced in the main inductor and thus reduces the switching noise. The new converter architecture also provides a unique design of the passive clamped circuit. This circuit is used to recycle the leakage energies of the coupled inductors which results in an efficiency improvement of the converter and to limit the voltage stress on the power switches. Circuit configuration, principles of operation and the transfer function are presented. The proposed concept is verified by the experimental and the simulated results of a range of case studies. The highest achieved efficiency observed in the experiments was 97.7%.

# Contents

|    | Ack                          | nowledgements                              | j                      |

|----|------------------------------|--------------------------------------------|------------------------|

|    | Aut                          | thor's Declaration                         | i                      |

|    | Abs                          | stract                                     | iii                    |

| Li | st of                        | Figures                                    | viii                   |

| Li | st of                        | Tables                                     | xv                     |

|    | Abl                          | previations                                | $\mathbf{x}\mathbf{v}$ |

| 1  | Intr                         | oduction                                   | 1                      |

|    | 1.1                          | Definitions                                | 3                      |

|    | 1.2                          | Introduction to Rectifier Circuits         | 6                      |

|    | 1.3                          | Introduction to Power Supplies             | 16                     |

|    |                              | 1.3.1 Linear Power Supplies                | 16                     |

|    |                              | 1.3.2 Switching Mode Power Supplies        | 18                     |

|    | 1.4                          | Thesis Aims and Organisation               | 27                     |

|    | 1.5                          | Contribution to Knowledge                  | 29                     |

| 2  | $\operatorname{Lit}\epsilon$ | erature Review                             | 31                     |

|    | 2.1                          | Single Phase Rectifier                     | 31                     |

|    |                              | 2.1.1 Research in the AC Side of Rectifier | 33                     |

|    |                              | 2.1.2 Research in the DC Side of Rectifier | 34                     |

|   | 2.2            | DC-DC Converters                                                  | 37  |

|---|----------------|-------------------------------------------------------------------|-----|

| 3 | AN             | Novel High Power Factor Single Phase Rectification Technique with |     |

|   | $\mathbf{Red}$ | luced Size DC Side Capacitor and Suppressed Line Current Har-     |     |

|   | mor            | nics                                                              | 40  |

|   | 3.1            | Introduction                                                      | 40  |

|   | 3.2            | The Proposed Technique                                            | 41  |

|   |                | 3.2.1 Circuit Configuration                                       | 41  |

|   |                | 3.2.2 Principles of Operation                                     | 42  |

|   | 3.3            | AC Side Analysis (Approximate Approach)                           | 48  |

|   | 3.4            | AC Side Analysis (Exact Approach)                                 | 59  |

|   | 3.5            | The Experimental Set-up                                           | 63  |

|   | 3.6            | Cases of Studies                                                  | 64  |

|   |                | 3.6.1 Conventional Single Phase Rectifier                         | 64  |

|   |                | 3.6.2 Proposed Single Phase Rectifier                             | 71  |

|   | 3.7            | Results and Discussion                                            | 80  |

|   | 3.8            | Summary                                                           | 83  |

| 4 | AN             | Novel Buck-Boost DC-DC Converter Using Close-Coupled Inductors    |     |

|   | and            | Passive Clamped Circuit                                           | 85  |

|   | 4.1            | Introduction                                                      | 85  |

|   | 4.2            | The Proposed Buck-Boost Converter                                 | 86  |

|   |                | 4.2.1 Circuit Configuration                                       | 86  |

|   |                | 4.2.2 Principles of Operation                                     | 86  |

|   | 4.3            | Transfer Function                                                 | 91  |

|   | 4.4            | Experimental Set-up                                               | 95  |

|   | 4.5            | Experimental Results of Case Studies                              | 96  |

|   |                | 4.5.1 Case Study 1                                                | 97  |

|   |                | 4.5.2 Case Study 2                                                | 99  |

|   | 4.6            | Simulated Results of Case Studies                                 | 102 |

|              |       | 4.6.1 Case Study 1                                                                      | 102          |

|--------------|-------|-----------------------------------------------------------------------------------------|--------------|

|              |       | 4.6.2 Case Study 2                                                                      | 102          |

|              | 4.7   | Experimental Results and Discussion                                                     | 107          |

|              | 4.8   | The Transient Response                                                                  | 108          |

|              | 4.9   | Summary                                                                                 | 110          |

| 5            | Cor   | nclusions and Future Work                                                               | 112          |

|              | 5.1   | Conclusions                                                                             | 112          |

|              | 5.2   | Future Work                                                                             | 118          |

|              |       | 5.2.1 The Rectification Technique Presented in Chapter $3 \dots \dots$ .                | 118          |

|              |       | 5.2.2 Buck-Boost DC-DC Converter Presented in Chapter 4                                 | 119          |

| P            | apers | s Published                                                                             | 121          |

| ${f A}$      | ppen  | ${ m Indix}\; {f A}\;\; { m Woodward}$ 's notation and the Harmonic Analysis of the Cor | 1-           |

|              | ven   | tional Single Phase Rectifier in Chapter 3                                              | 145          |

|              | A.1   | Woodward's notation                                                                     | 145          |

|              | A.2   | Harmonic Analysis of the Conventional Single Phase Rectifier in Chapter                 | 3147         |

| ${f A}$      | ppen  | ndix B Wolfram Mathematica Codes                                                        | 150          |

| ${f A}$      | ppen  | ndix C The Layout of the Prototype Circuits in Chapter 3                                | 157          |

| ${f A}$      | ppen  | ndix D The Layout of the Prototype Circuit and the Simulatio                            | $\mathbf{n}$ |

|              | Mo    | del in Chapter 4                                                                        | 160          |

| $\mathbf{A}$ | ppen  | ndix E Practical case studies of the proposed buck-boost DC-D                           | ${f C}$      |

|              | con   | verter in Chapter 4                                                                     | 163          |

|              | E.1   | Case Study 3                                                                            | 163          |

|              | E.2   | Case Study 4                                                                            | 163          |

| ${f A}$      | ppen  | ndix F Simulated case studies of the proposed buck-boost DC-D                           | ${f C}$      |

|              | con   | verter in Chapter 4                                                                     | 168          |

| F.1     | Case Study 3                                                          | 168          |

|---------|-----------------------------------------------------------------------|--------------|

| F.2     | Case Study 4                                                          | 168          |

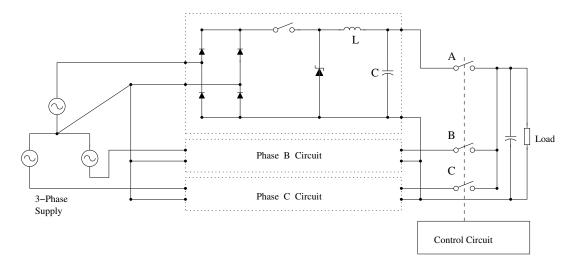

| Appen   | dix G A New Three Phase Buck Converter Using Three-Single             | $\mathbf{e}$ |

| Mod     | dules of Single Phase Buck Converters                                 | 173          |

| G.1     | Introduction                                                          | 173          |

| G.2     | Three-Phase Buck Converter Using Three-Single Modules of Single-Phase |              |

|         | Buck Converters                                                       | 176          |

|         | G.2.1 Circuit Configuration                                           | 176          |

|         | G.2.2 Principles of Operation                                         | 177          |

| G.3     | The Experimental Set-up                                               | 177          |

| G.4     | Experimental Results of Cases Studies                                 | 178          |

|         | G.4.1 Conventional three-phase buck converter                         | 178          |

|         | G.4.2 Proposed three-phase buck converter                             | 179          |

| G.5     | Summary and Conclusions                                               | 180          |

| Bibliog | graphy                                                                | 186          |

# List of Figures

| 1.1  | Block Diagram of Power Electronic System                              | 2  |

|------|-----------------------------------------------------------------------|----|

| 1.2  | A Single Phase Half-Wave Rectifier                                    | 6  |

| 1.3  | A Single Phase Centre-Tapped Transformer Full-Wave Rectifier          | 7  |

| 1.4  | A Single Phase Full-Wave Bridge Rectifier                             | 7  |

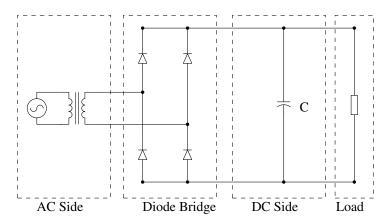

| 1.5  | A Single Phase Full-Wave Bridge Rectifier with Capacitor Filter       | 8  |

| 1.6  | Load Voltage without DC Side Capacitor                                | 9  |

| 1.7  | Load Voltage with DC Side Capacitor                                   | 9  |

| 1.8  | Sketch of Equation (1.14)                                             | 10 |

| 1.9  | Nomogram for Solving Equation (1.14)                                  | 11 |

| 1.10 | Sketch of Equation (1.14) with Straight Line Approximation            | 12 |

| 1.11 | Generic Supply Voltage and the Line Current Waveforms of the Single   |    |

|      | Phase Bridge Rectifier with Capacitor Filter                          | 15 |

| 1.12 | Shunt Regulator                                                       | 17 |

| 1.13 | Series Regulator                                                      | 17 |

| 1.14 | Step-Down or Buck Converter                                           | 18 |

| 1.15 | On State Circuit Diagram                                              | 21 |

| 1.16 | Off State Circuit Diagram                                             | 21 |

| 1.17 | Inductor Current at On State                                          | 21 |

| 1.18 | Inductor Current at Off State                                         | 21 |

| 1.19 | An Approximate Capacitor Ripple Voltage and Current with the Inductor |    |

|      | Current                                                               | 22 |

| 1.20 | Step-Up or Boost Converter                                            | 24 |

| 1.21 | Step-Up-Down Converter                                                   | 25 |

|------|--------------------------------------------------------------------------|----|

| 1.22 | Weinberg Converter                                                       | 26 |

| 2.1  | Single Phase Bridge Rectifier with Marked Regions of Research Groups .   | 32 |

| 2.2  | Valley Fill Circuit                                                      | 36 |

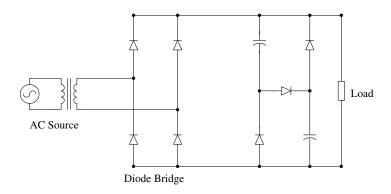

| 2.3  | Theoretical Waveforms of the Valley Fill Circuit                         | 36 |

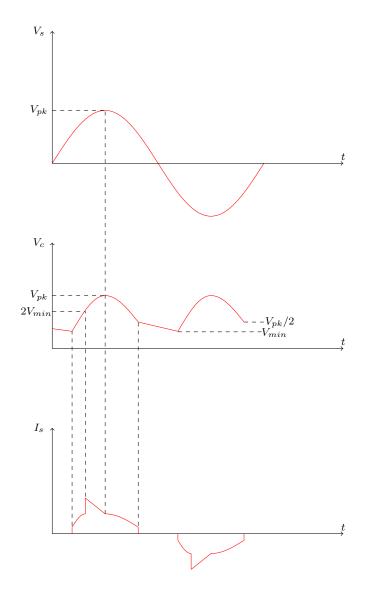

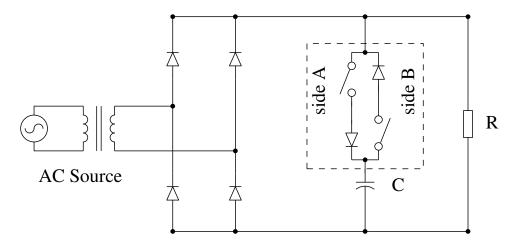

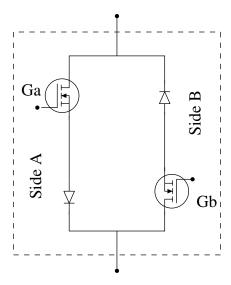

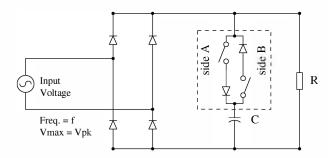

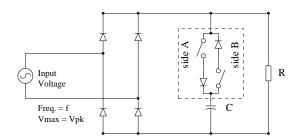

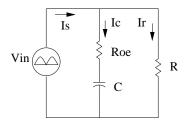

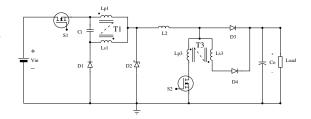

| 3.1  | Circuit Configuration of the Proposed Single-Phase Rectifier             | 41 |

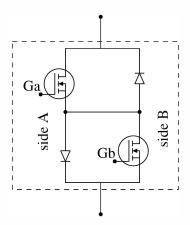

| 3.2  | Structure of the Proposed Bidirectional Switch                           | 42 |

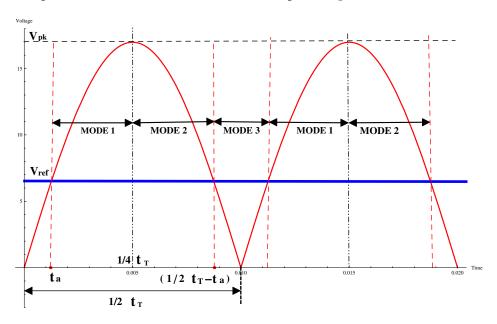

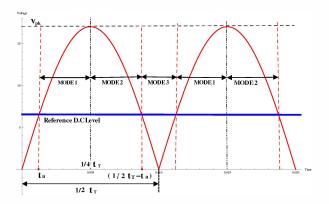

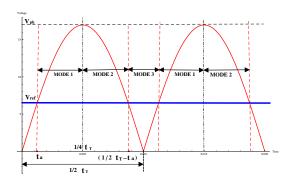

| 3.3  | Operating Zones of The Proposed Technique                                | 42 |

| 3.4  | Equivalent Circuit of The Rectifier at Mode 1                            | 43 |

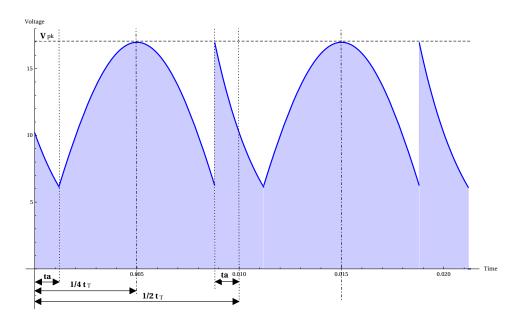

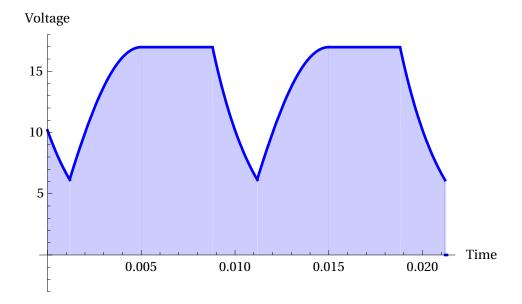

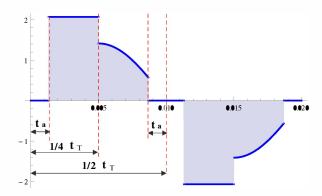

| 3.5  | Analytical Rectifier Output Voltage Waveform with the Proposed Technique | 47 |

| 3.6  | Analytical Capacitor Voltage Waveform with the Proposed Technique        | 47 |

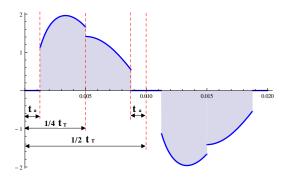

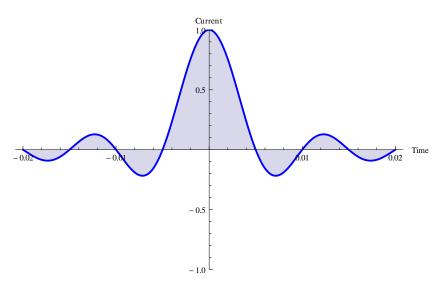

| 3.7  | Analytical Rectifier Line Current Waveform with the Proposed Technique   |    |

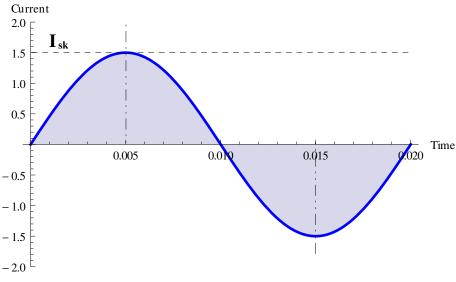

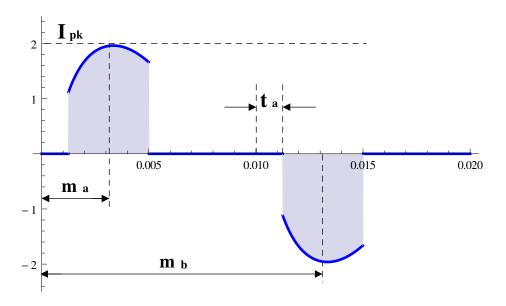

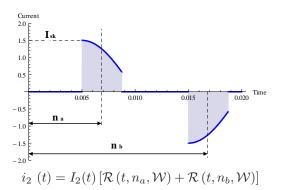

|      | (Approx.)                                                                | 48 |

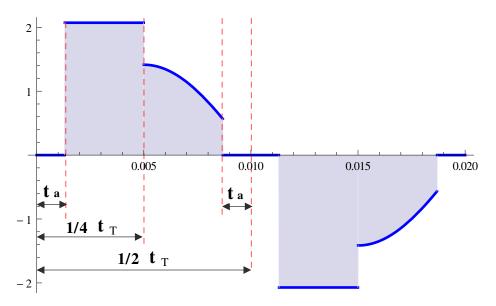

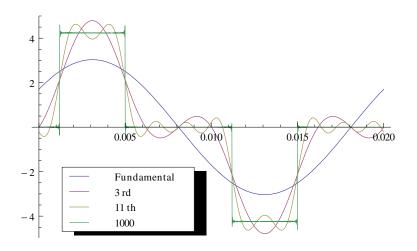

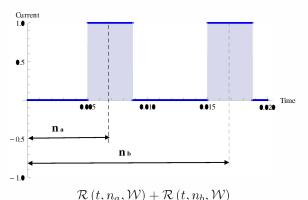

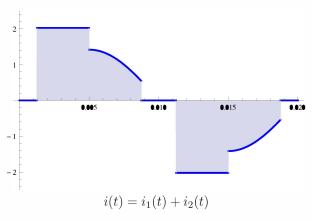

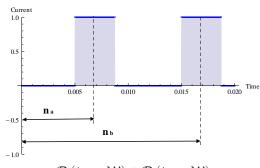

| 3.8  | Pure Sinusoid Waveform                                                   | 50 |

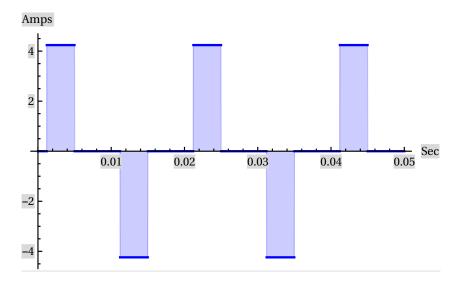

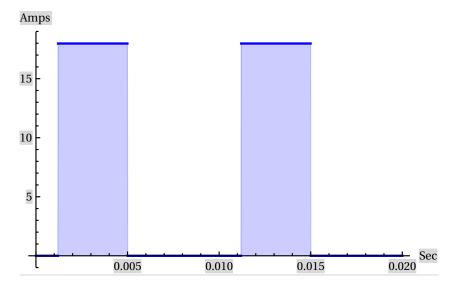

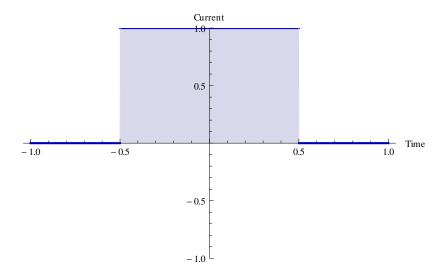

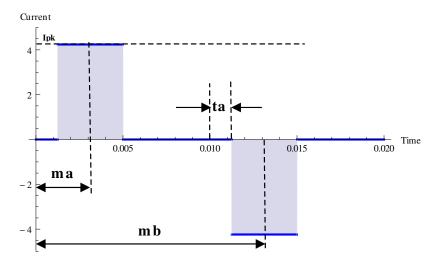

| 3.9  | Unity Amplitude Rect Pulses                                              | 50 |

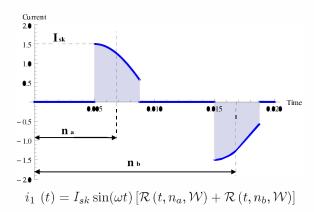

| 3.10 | Sinusoid Multiplied By Unity Amplitude Rect Pulses                       | 51 |

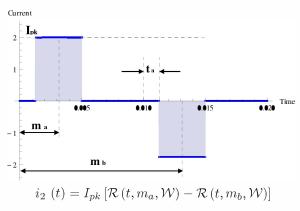

| 3.11 | Rect Pulses of the Rectangular Segments of the Line Current              | 51 |

| 3.12 | Analytical Rectifier Line Current Waveform with the Proposed Technique   |    |

|      | (Exact)                                                                  | 59 |

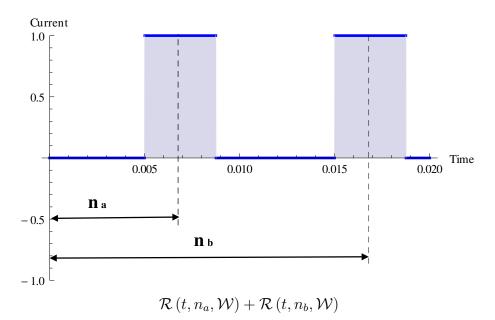

| 3.13 | Sinusoid Multiplied by Unity Amplitude Rect Pulses                       | 61 |

| 3.14 | Rect Pulses of the Line Current in Mode 1                                | 62 |

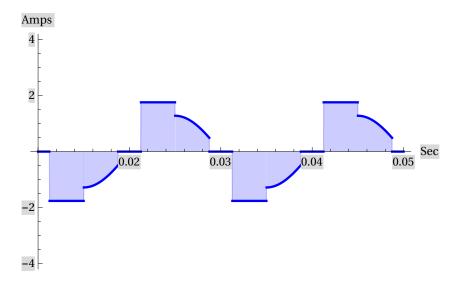

| 3.15 | Analytical Line Current Waveform of the Conventional Rectifier           | 65 |

| 3.16 | Analytical Squared Line Current Waveform of the Conventional Rectifier   | 65 |

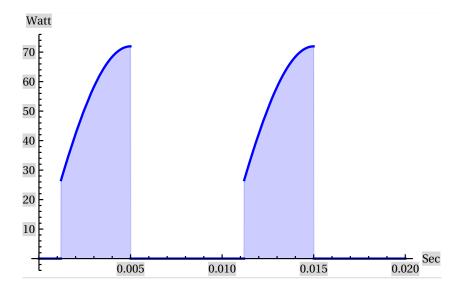

| 3.17 | Analytical Instantaneous Input Power Waveform of the Conventional Rec-   |    |

|      | tifier                                                                   | 66 |

| 3.18 | Analytical Displacement Angle of the Conventional Rectifier              | 67 |

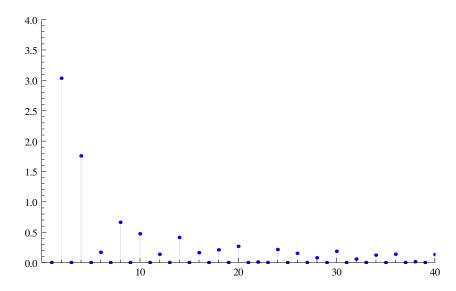

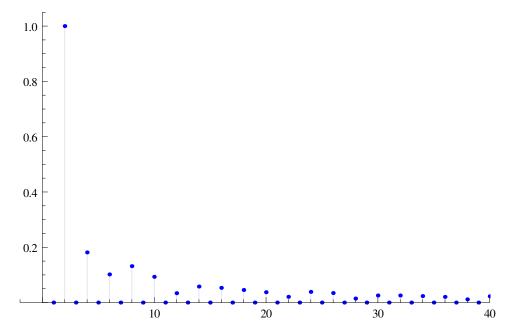

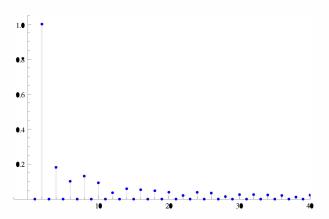

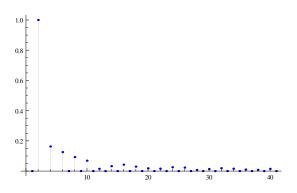

| 3.19 | Fourier Analysis of the Line Current of the Conventional Rectifier       | 68 |

| 3.20 | Analytical Frequency Spectrum of the Line Current of the Conventional   |    |

|------|-------------------------------------------------------------------------|----|

|      | Rectifier                                                               | 68 |

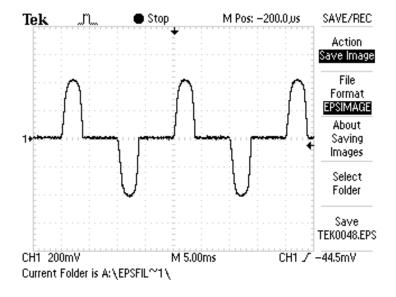

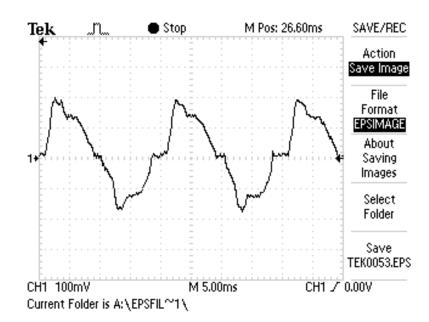

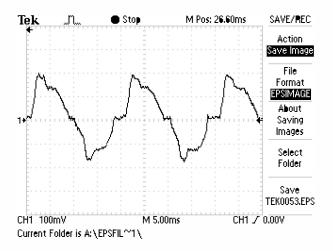

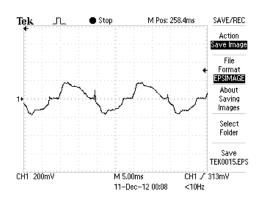

| 3.21 | Experimental Line Current Waveform of the Conventional Rectifier        | 69 |

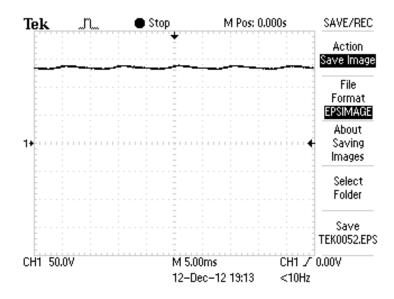

| 3.22 | Experimental Output Voltage Waveform of the Conventional Rectifier      | 70 |

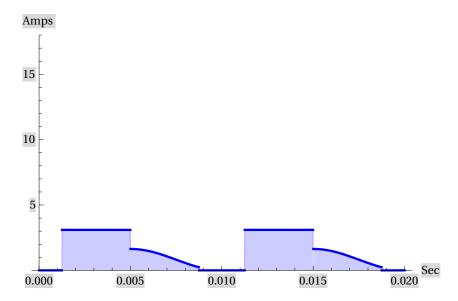

| 3.23 | Analytical Line Current Waveform of the Proposed Rectifier              | 71 |

| 3.24 | Analytical Squared Line Current Waveform of the Proposed Rectifier      | 72 |

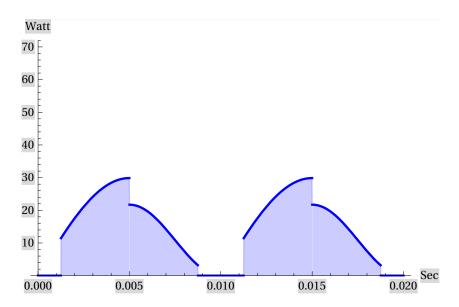

| 3.25 | Analytical Instantaneous Input Power Waveform of the Proposed Rectifier | 73 |

| 3.26 | Analytical Displacement Angle of the Proposed Rectifier                 | 74 |

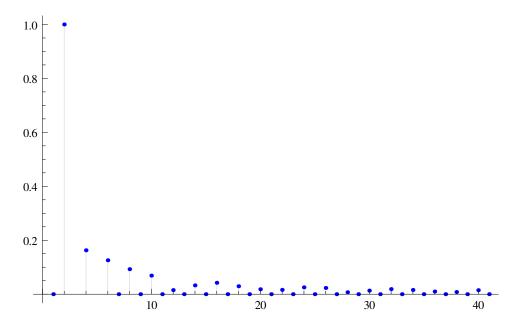

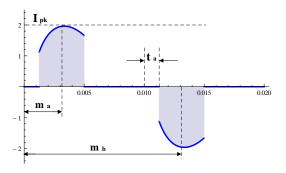

| 3.27 | Fourier Analysis of the line Current of Proposed Rectifier              | 75 |

| 3.28 | Frequency Spectrum of the Line Current with Approximate Approach        | 75 |

| 3.29 | Frequency Spectrum of the Line Current with Exact Approach              | 76 |

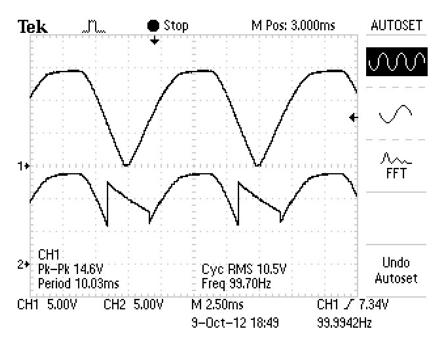

| 3.30 | Experimental Line Current Waveform of the Proposed Rectifier            | 77 |

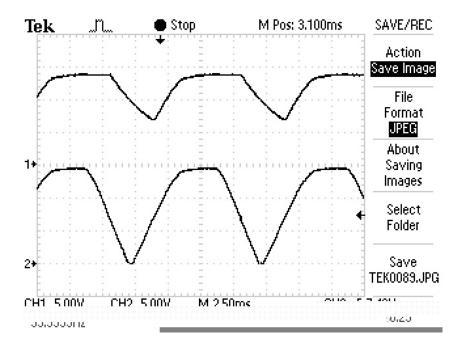

| 3.31 | Experimental Supply Voltage and the Output Voltage Waveforms            | 78 |

| 3.32 | Experimental Capacitor Voltage and the Supply Voltage Waveforms         | 79 |

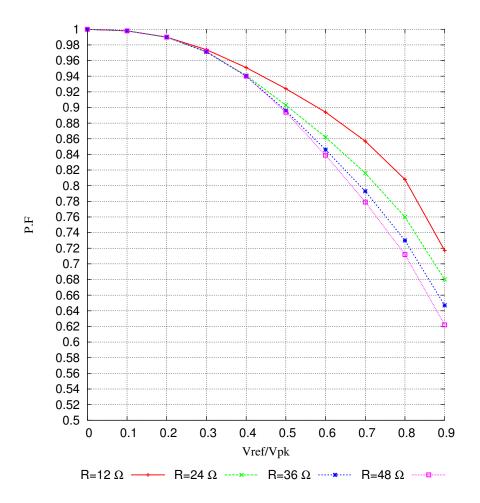

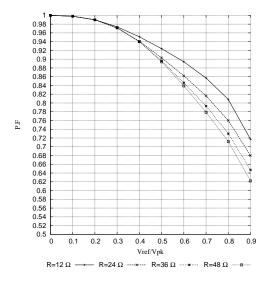

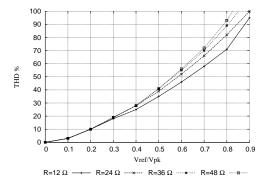

| 3.33 | Power Factor vs the Voltage Ratio $(V_{ref}/V_{pk})$                    | 80 |

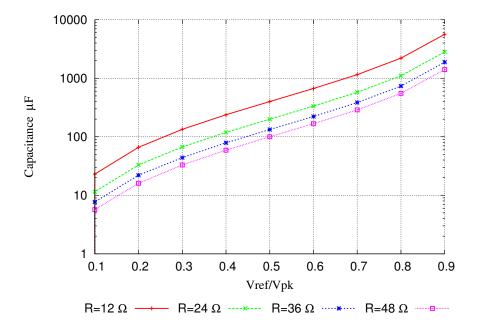

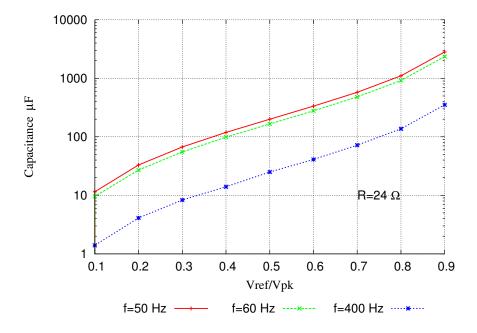

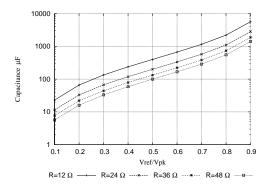

| 3.34 | The DC Side Capacitor Size vs the Voltage Ratio $(V_{ref}/V_{pk})$      | 81 |

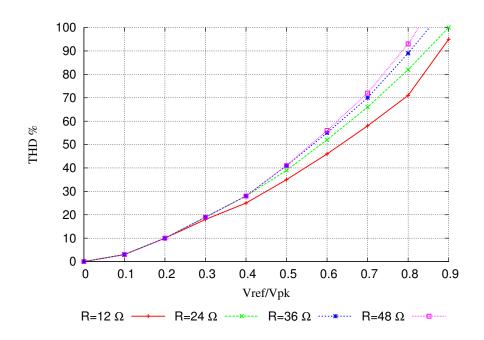

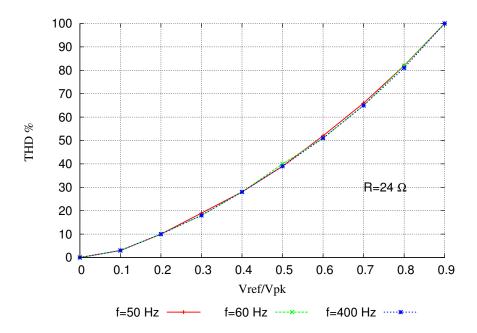

| 3.35 | The THD vs the Voltage Ratio $(V_{ref}/V_{pk})$                         | 82 |

| 3.36 | The DC Side Capacitor Size vs the Line Frequency                        | 82 |

| 3.37 | The THD vs the Line Frequency                                           | 83 |

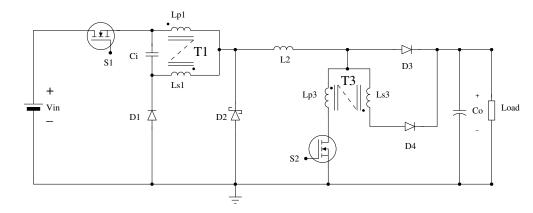

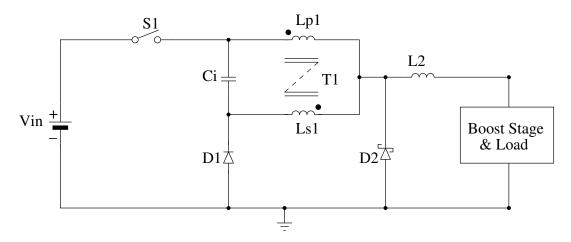

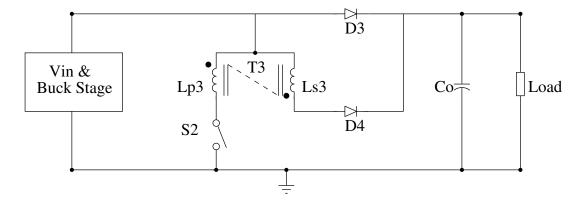

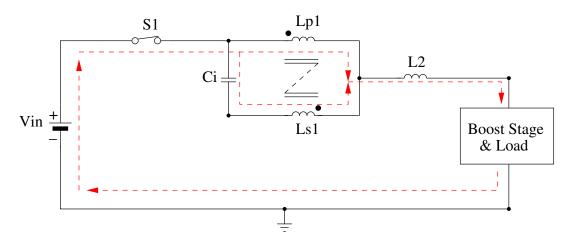

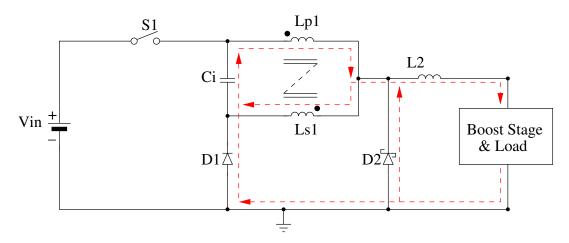

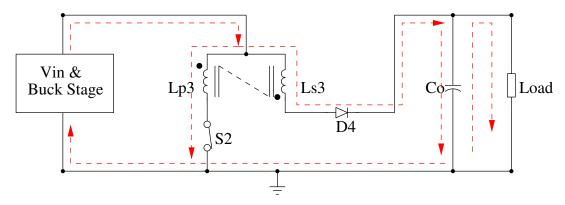

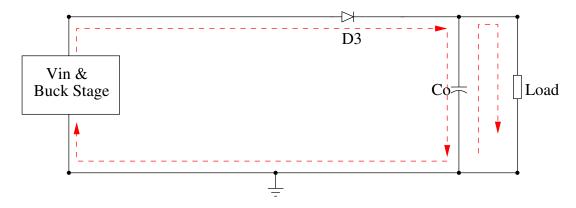

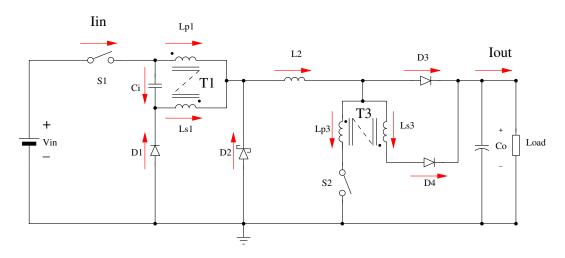

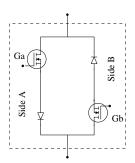

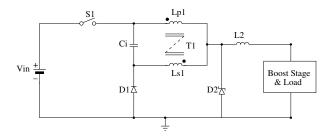

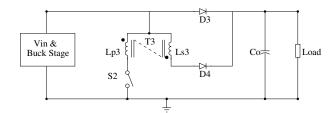

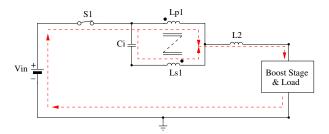

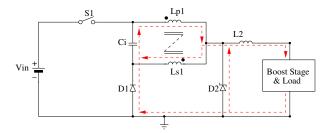

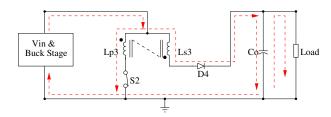

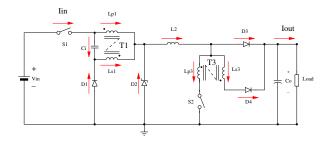

| 4.1  | Circuit Configuration of the Proposed Buck-Boost DC-DC Converter        | 86 |

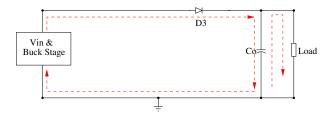

| 4.2  | Buck Stage of the Proposed Buck-Boost DC-DC Converter                   | 87 |

| 4.3  | Boost Stage of the Proposed Buck-Boost DC-DC Converter                  | 87 |

| 4.4  | On State of Buck Stage                                                  | 88 |

| 4.5  | Off State of Buck Stage                                                 | 89 |

| 4.6  | On State of Boost Stage                                                 | 90 |

| 4.7  | Off State of Boost Stage                                                | 90 |

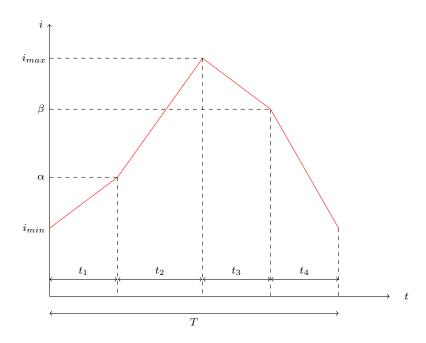

| 4.8  | Inductor Current Waveform                                               | 92 |

| 4.9  | Circuit Configuration of the Proposed Converter with All Currents Paths | 97 |

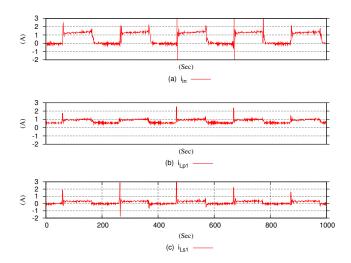

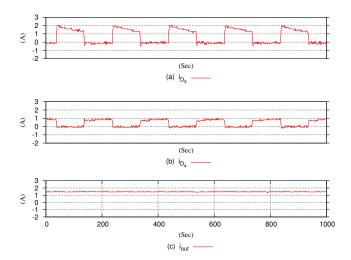

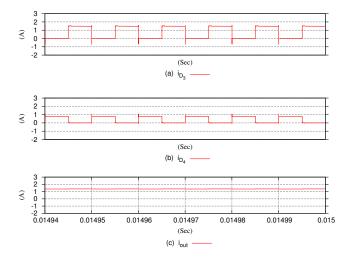

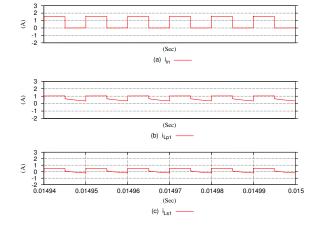

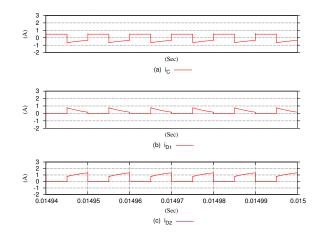

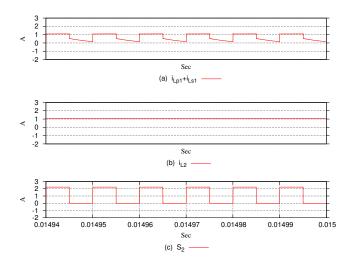

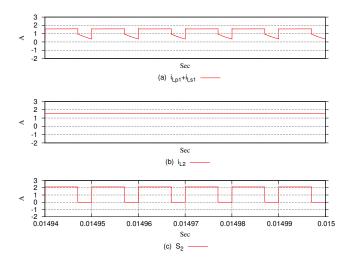

| 4.10 | Experimental Current Waveforms of Case Study 1: (a) input current, (b)             |     |

|------|------------------------------------------------------------------------------------|-----|

|      | primary winding current of $T_1$ , (c) secondary winding current of $T_1$          | 97  |

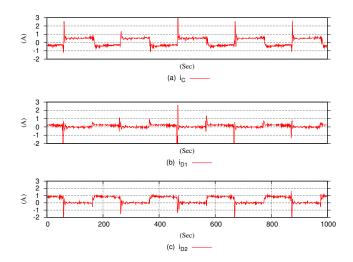

| 4.11 | Experimental Current Waveforms of Case Study 1: (a) current of capacitor           |     |

|      | $C_i$ , (b) current of diode $D_1$ , (c) current of diode $D_2$ ,                  | 98  |

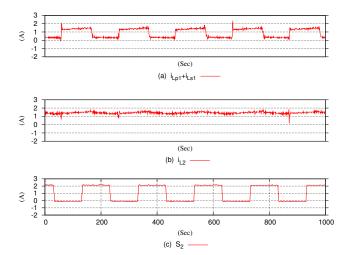

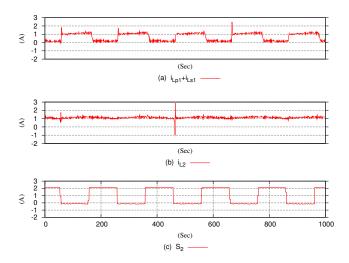

| 4.12 | Experimental Current Waveforms of Case Study 1: (a) primary and sec-               |     |

|      | ondary winding currents of $T_1$ , (b) main inductor current $L_2$ , (c) switching |     |

|      | signal of switch $S_2$                                                             | 98  |

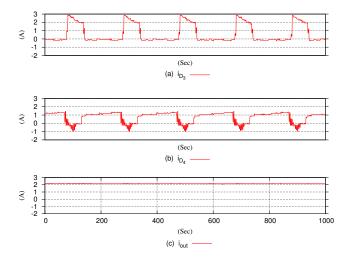

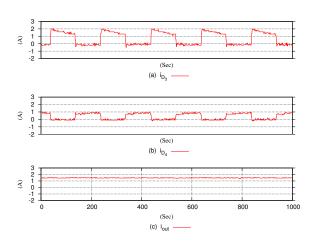

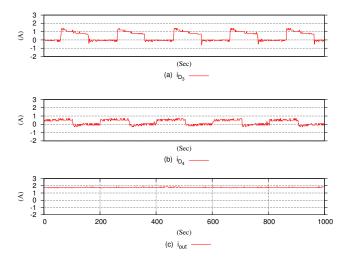

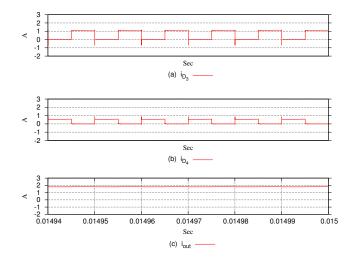

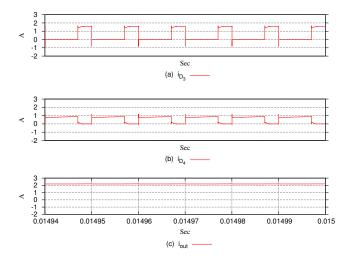

| 4.13 | Experimental Current Waveforms of Case Study 1: (a) current of diode               |     |

|      | $D_3$ , (b) current of diode $D_4$ , (c) output current $i_{out}$                  | 99  |

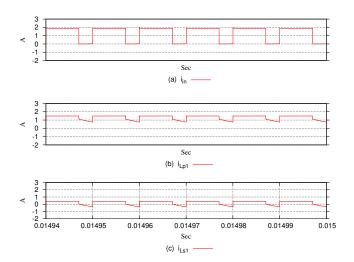

| 4.14 | Experimental Current Waveforms of Case Study 2: (a) input current, (b)             |     |

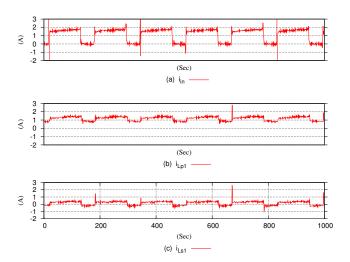

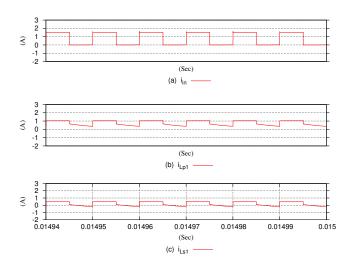

|      | primary winding current of $T_1$ , (c) secondary winding current of $T_1$          | 100 |

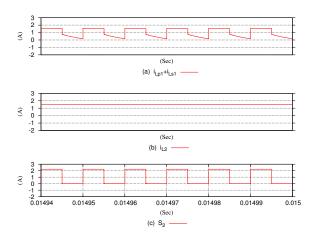

| 4.15 | Experimental Current Waveforms of Case Study 2: (a) current of capacitor           |     |

|      | $C_i$ , (b) current of diode $D_1$ , (c) current of diode $D_2$ ,                  | 100 |

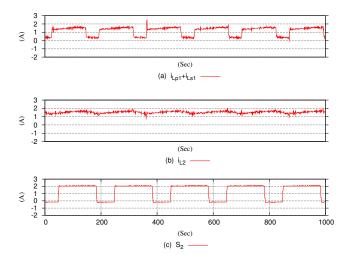

| 4.16 | Experimental Current Waveforms of Case Study 2: (a) primary and sec-               |     |

|      | ondary winding currents of $T_1$ , (b) main inductor current $L_2$ , (c) switching |     |

|      | signal of switch $S_2$                                                             | 101 |

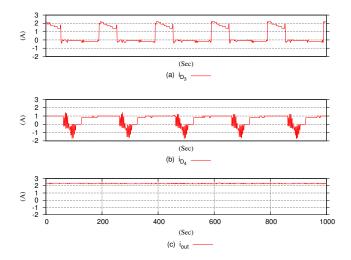

| 4.17 | Experimental Current Waveforms of Case Study 2: (a) current of diode               |     |

|      | $D_3$ , (b) current of diode $D_4$ , (c) output current $i_{out}$                  | 101 |

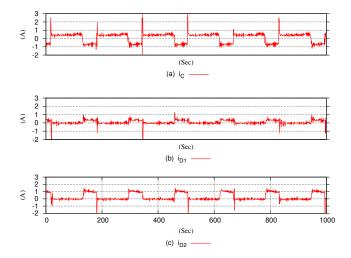

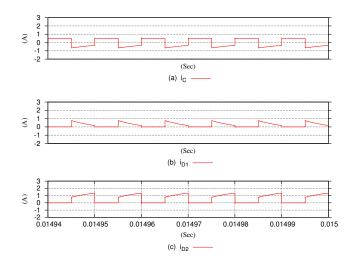

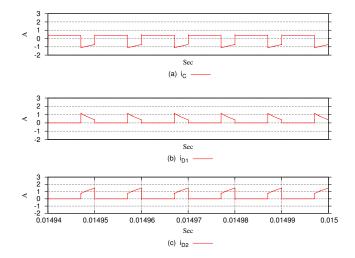

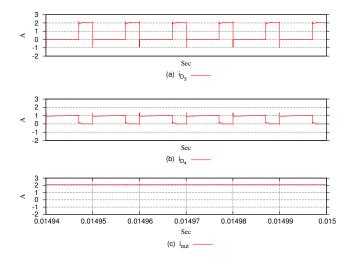

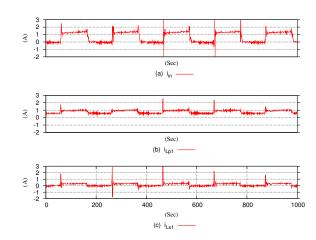

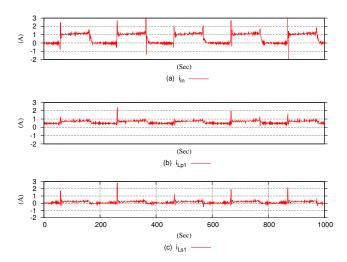

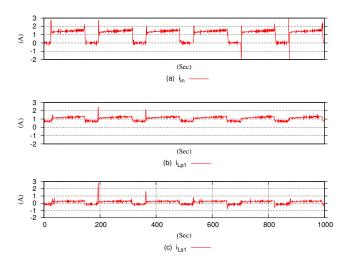

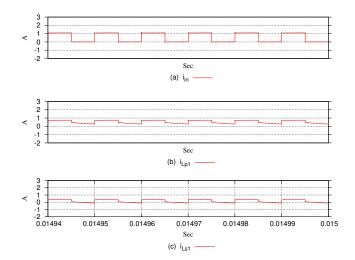

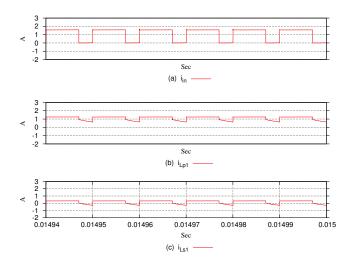

| 4.18 | Simulated Current Waveforms of Case Study 1: (a) input current, (b)                |     |

|      | primary winding current of $T_1$ , (c) secondary winding current of $T_1$          | 103 |

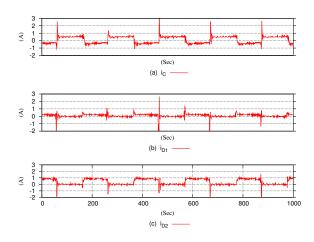

| 4.19 | Simulated Current Waveforms of Case Study 1: (a) current of capacitor              |     |

|      | $C_i$ , (b) current of diode $D_1$ , (c) current of diode $D_2$ ,                  | 103 |

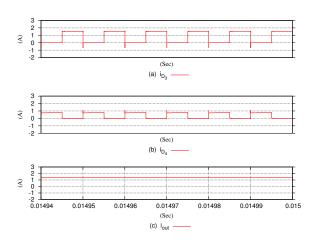

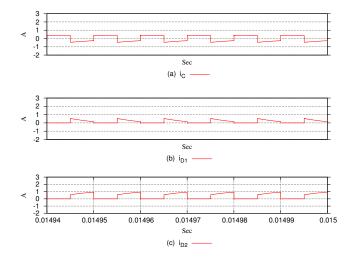

| 4.20 | Simulated Current Waveforms of Case Study 1: (a) primary and secondary             |     |

|      | winding currents of $T_1$ , (b) main inductor current $L_2$ , (c) switching signal |     |

|      | of switch $S_2$                                                                    | 104 |

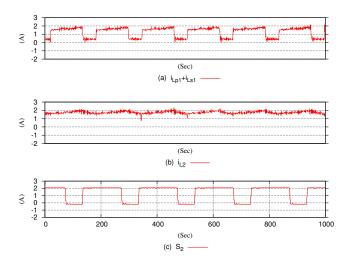

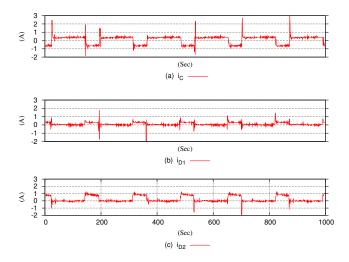

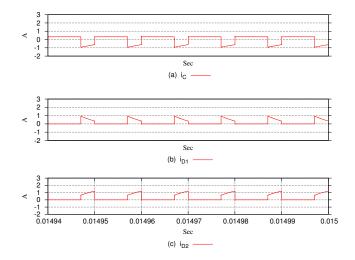

| 4.21 | Simulated Current Waveforms of Case Study 1: (a) current of diode $D_3$ ,          |     |

|      | (b) current of diode $D_4$ , (c) output current $i_{out}$                          | 104 |

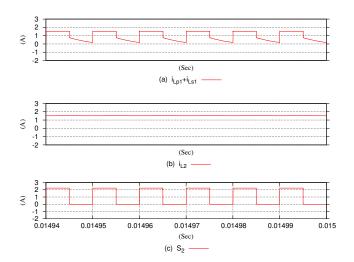

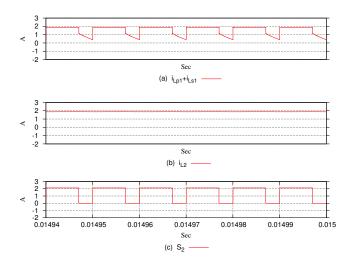

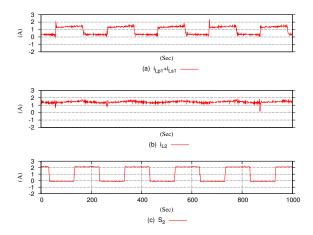

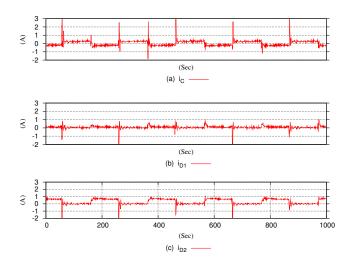

| 4.22 | Simulated Current Waveforms of Case Study 2: (a) input current, (b)                |     |

|      | primary winding current of $T_1$ , (c) secondary winding current of $T_1$          | 105 |

| 4.25 | Simulated Current wavelorms of Case Study 2: (a) current of capacitor              |     |

|------|------------------------------------------------------------------------------------|-----|

|      | $C_i$ , (b) current of diode $D_1$ , (c) current of diode $D_2$ ,                  | 105 |

| 4.24 | Simulated Current Waveforms of Case Study 2: (a) primary and secondary             |     |

|      | winding currents of $T_1$ , (b) main inductor current $L_2$ , (c) switching signal |     |

|      | of switch $S_2$                                                                    | 106 |

| 4.25 | Simulated Current Waveforms of Case Study 2: (a) current of diode $D_3$ ,          |     |

|      | (b) current of diode $D_4$ , (c) output current $i_{out}$                          | 106 |

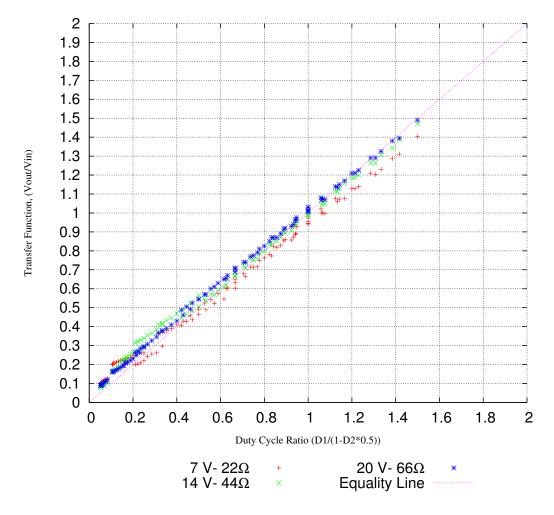

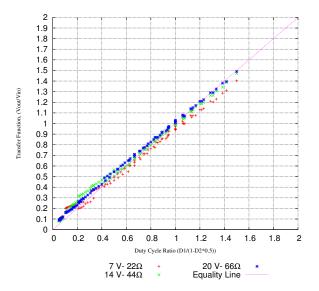

| 4.26 | Experimental Results of a Range of Case Studies                                    | 107 |

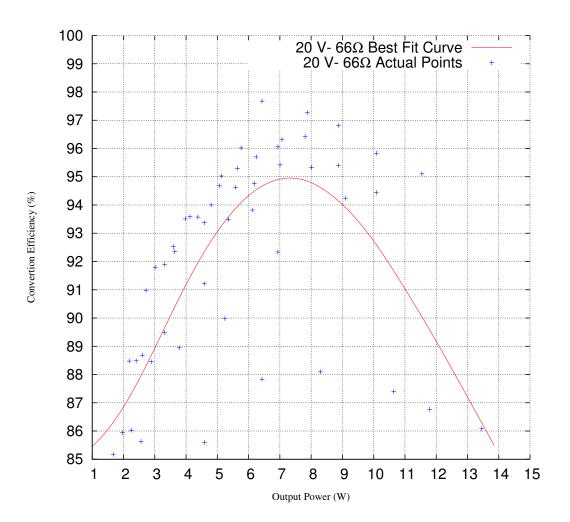

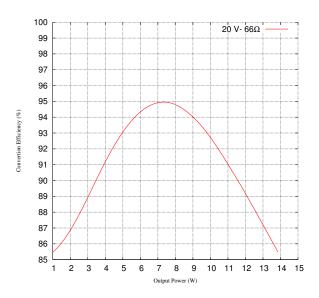

| 4.27 | Measured Efficiency Versus Output Power                                            | 109 |

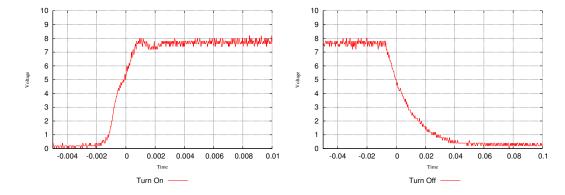

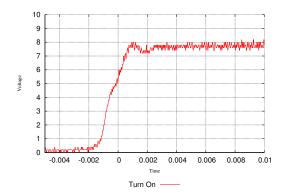

| 4.28 | Turn On Transient                                                                  | 109 |

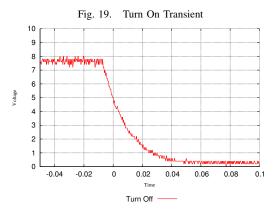

| 4.29 | Turn Off Transient                                                                 | 109 |

| A.1  | The Rect Waveform                                                                  | 146 |

| A.2  | The Sinc Waveform                                                                  | 146 |

| A.3  | Analytical Input Current Waveform of the Conventional Rectifier                    | 147 |

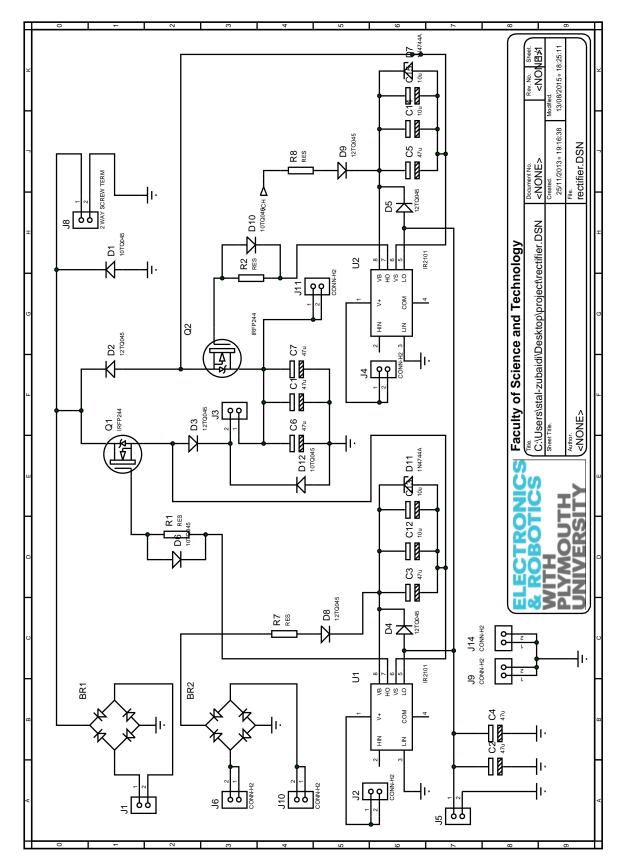

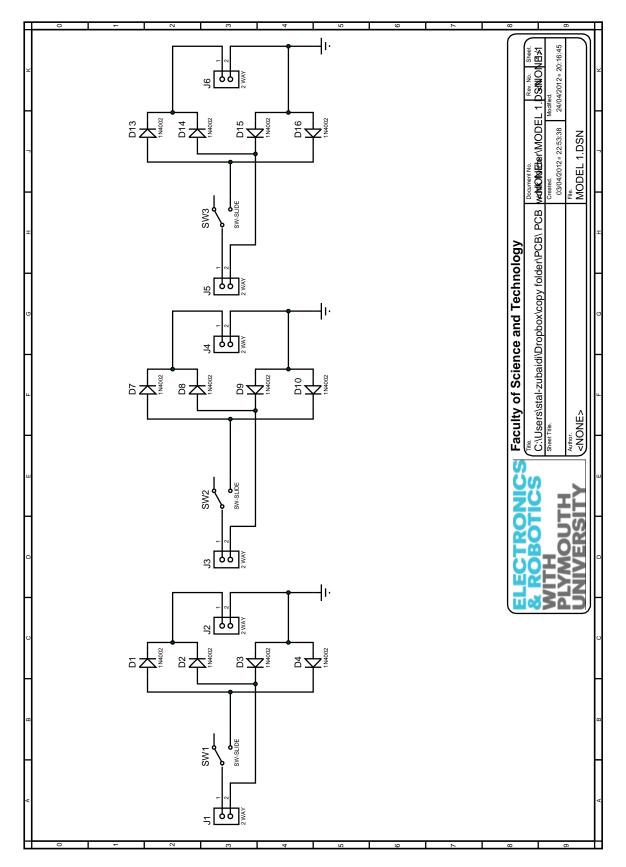

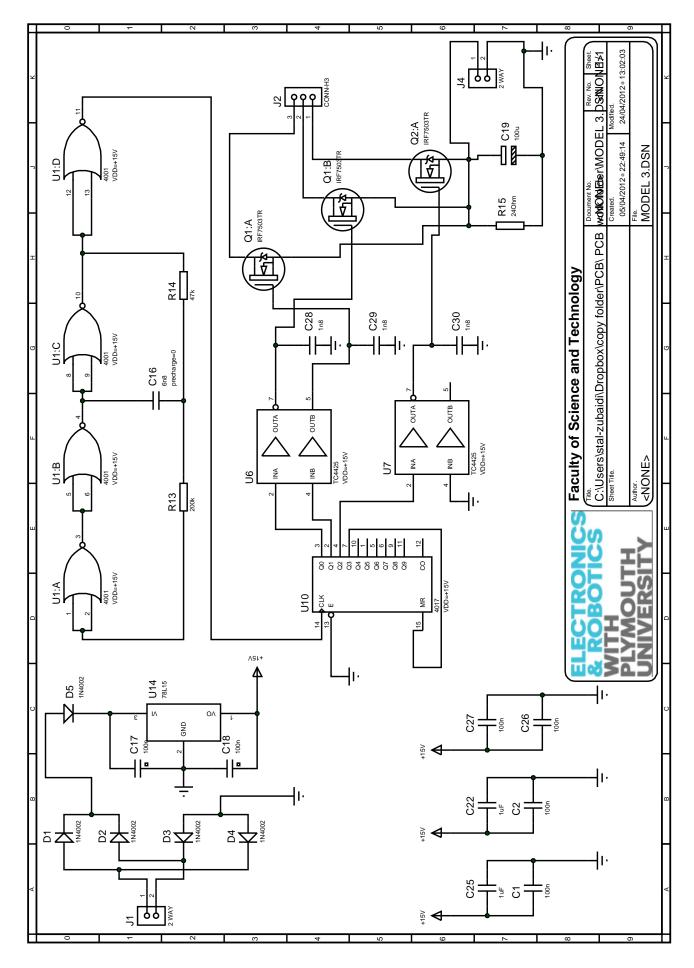

| C.1  | The Layout of the Prototype Circuit of the Proposed Single Phase Rectified         | 158 |

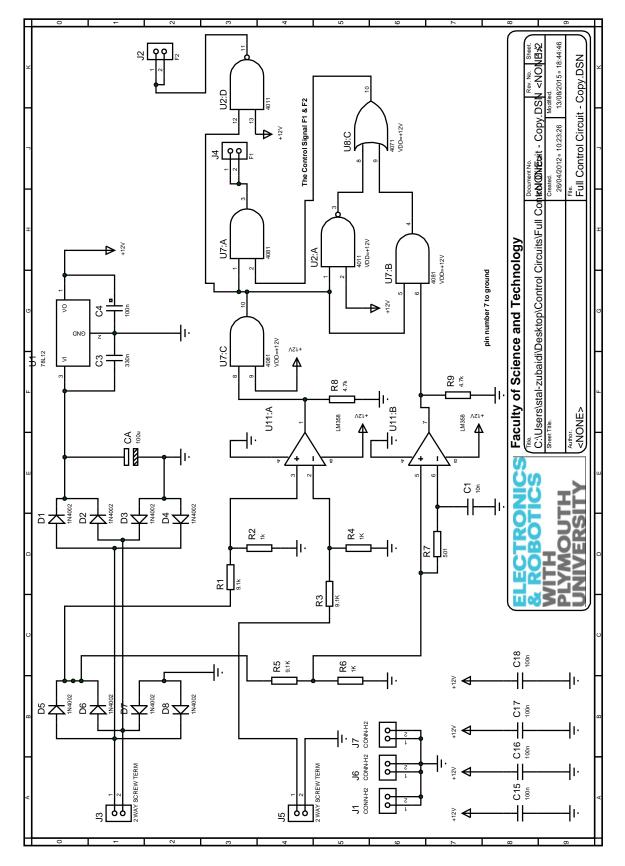

| C.2  | The Layout of the Prototype Circuit of the Proposed Control Scheme for             |     |

|      | the New Rectifier System                                                           | 159 |

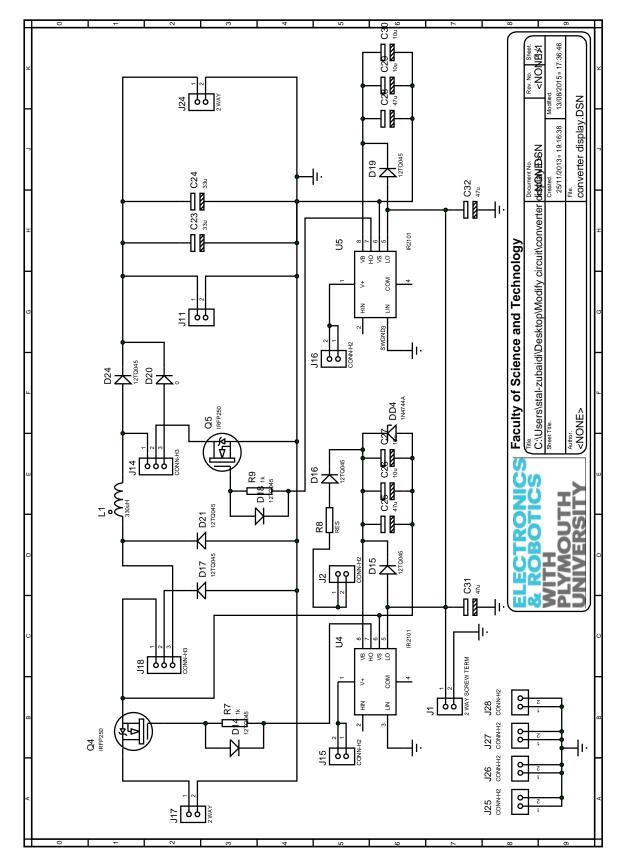

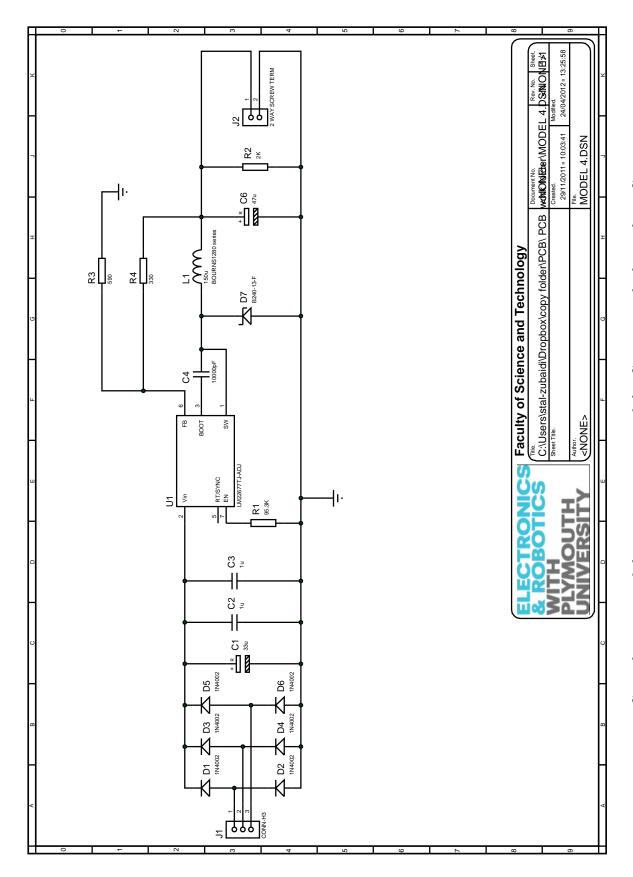

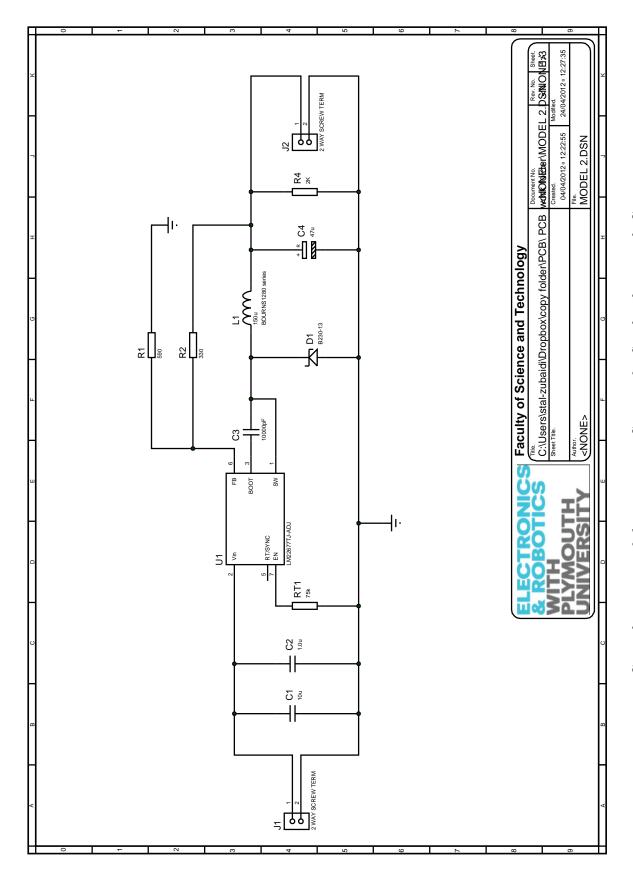

| D.1  | The Layout of the Prototype Circuit of the Proposed Buck-Boost DC-DC               |     |

|      | Converter                                                                          | 161 |

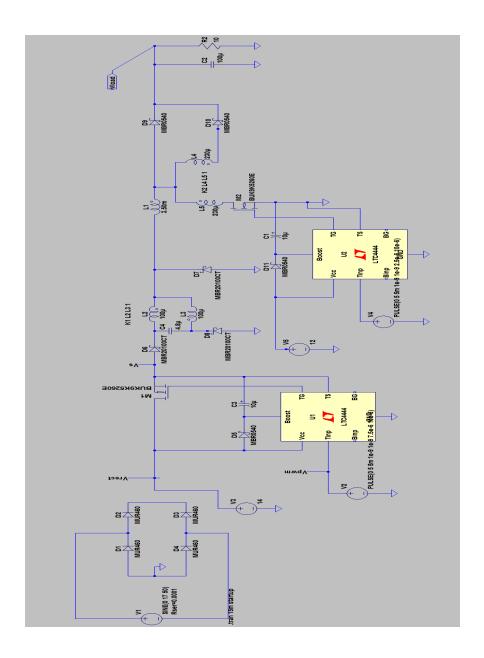

| D.2  | The Layout of the Simulation Model of the Proposed Buck-Boost DC-DC                |     |

|      | Converter                                                                          | 162 |

| E.1  | Experimental Current Waveforms of Case Study 3: (a) input current, (b)             |     |

|      | primary winding current of $T_1$ , (c) secondary winding current of $T_1$          | 164 |

| E.2  | Experimental Current Waveforms of Case Study 3: (a) current of capacitor           |     |

|      | $C_i$ , (b) current of diode $D_1$ , (c) current of diode $D_2$ ,                  | 164 |

| E.3  | Experimental Current Waveforms of Case Study 3: (a) primary and sec-               |     |

|      | ondary winding currents of $T_1$ , (b) main inductor current $L_2$ , (c) switching |     |

|      | signal of switch $S_2$                                                             | 165 |

| L.4 | Experimental Current waveforms of Case Study 3: (a) current of diode               |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | $D_3$ , (b) current of diode $D_4$ , (c) output current $i_{out}$                  | 165 |

| E.5 | Experimental Current Waveforms of Case Study 4: (a) input current, (b)             |     |

|     | primary winding current of $T_1$ , (c) secondary winding current of $T_1$          | 166 |

| E.6 | Experimental Current Waveforms of Case Study 4: (a) current of capacitor           |     |

|     | $C_i$ , (b) current of diode $D_1$ , (c) current of diode $D_2$ ,                  | 166 |

| E.7 | Experimental Current Waveforms of Case Study 4: (a) primary and sec-               |     |

|     | ondary winding currents of $T_1$ , (b) main inductor current $L_2$ , (c) switching |     |

|     | signal of switch $S_2$                                                             | 167 |

| E.8 | Experimental Current Waveforms of Case Study 4: (a) current of diode               |     |

|     | $D_3$ , (b) current of diode $D_4$ , (c) output current $i_{out}$                  | 167 |

| F.1 | Simulated Current Waveforms of Case Study 3: (a) input current, (b)                |     |

|     | primary winding current of $T_1$ , (c) secondary winding current of $T_1$          | 169 |

| F.2 | Simulated Current Waveforms of Case Study 3: (a) current of capacitor              |     |

|     | $C_i$ , (b) current of diode $D_1$ , (c) current of diode $D_2$ ,                  | 169 |

| F.3 | Simulated Current Waveforms of Case Study 3: (a) primary and secondary             |     |

|     | winding currents of $T_1$ , (b) main inductor current $L_2$ , (c) switching signal |     |

|     | of switch $S_2$                                                                    | 170 |

| F.4 | Simulated Current Waveforms of Case Study 3: (a) current of diode $D_3$ ,          |     |

|     | (b) current of diode $D_4$ , (c) output current $i_{out}$                          | 170 |

| F.5 | Simulated Current Waveforms of Case Study 4: (a) input current, (b)                |     |

|     | primary winding current of $T_1$ , (c) secondary winding current of $T_1$          | 171 |

| F.6 | Simulated Current Waveforms of Case Study 4: (a) current of capacitor              |     |

|     | $C_i$ , (b) current of diode $D_1$ , (c) current of diode $D_2$ ,                  | 171 |

| F.7 | Simulated Current Waveforms of Case Study 4: (a) primary and secondary             |     |

|     | winding currents of $T_1$ , (b) main inductor current $L_2$ , (c) switching signal |     |

|     | of switch $S_2$                                                                    | 172 |

| F.8 | Simulated Current Waveforms of Case Study 4: (a) current of diode $D_3$ ,          |     |

|     | (b) current of diode $D_4$ , (c) output current $i_{out}$                          | 172 |

| G.1 | Proposed Three-Single Phase Buck-Type Converter                           | 176 |

|-----|---------------------------------------------------------------------------|-----|

| G.2 | The Layout of the prototype circuit of the Conventional Three Phase       |     |

|     | Converter                                                                 | 182 |

| G.3 | The Layout of the Prototype Circuit of the Three-Single Modules of Single |     |

|     | Phase Rectifiers                                                          | 183 |

| G.4 | The Layout of the Prototype Circuit of a Single Phase Buck Converter .    | 184 |

| G.5 | The Layout of the Prototype Circuit of the Proposed Control Scheme for    |     |

|     | the New Converter System                                                  | 185 |

# List of Tables

| 3.1 | The Design Parameters                       | 41 |

|-----|---------------------------------------------|----|

| 3.2 | Applied Design Parameters of the Case Study | 77 |

| 4.1 | Experimental Set-up Parameters              | 96 |

| 4.2 | Cases Studies Testing Conditions            | 96 |

# Abbreviations

**CCM** Continuous Conduction Mode

$disp_f$  Displacement Factor

$dist_f$  Distortion Factor

e.m.f Electromotive Force

**EMI** Electromagnetic Interference

**PF** Power Factor

**PFC** Power Factor Correction

**PWM** Pulse Width Modulation

rms Root Mean Square

**THD** Total Harmonics Distortion

**ZCS** Zero Current Switching

**ZVS** Zero Voltage Switching

# Chapter 1

### Introduction

The demand for energy, particularly in electrical form is ever increasing in order to improve the standard of the modern life. Power electronics has already found an important place in modern technology and been used in wide range of applications.

Power electronics can be defined as the application of solid-state electronics for the control and conversion of electric power [1]. Power electronic systems convert electrical energy from the form supplied by a source to the form required by a load. For example, the part of a computer that takes the AC mains voltage and changes it into the 5 V DC required by the logic chip is a power electronic circuit [2].

The main objectives of the power electronics is to process and control the flow of electrical power between a source and a load by supplying an optimally suited voltages and currents for the connected loads [3].

This control involve not just changing the amount of the transmitted power, but it may include changing the nature of the delivered power to the load as in AC to DC or DC to AC conversion processes, or changing the frequency of the AC power as required by the load. [4].

Power electronics has developed rapidly in recent years due to the development of the solid-state electronics devices that are able to switch large currents and withstand large voltages [5].

As the voltage and current ratings and switching characteristics of power semiconductor devices keep improving, the range of applications continue to expand in different areas from hundreds of megawatts down to a few watts for domestics applications. lamp controls; power supplies; industrial drives; transportation; energy storage and electric power transmission and distribution are some of these applications [1,3].

In any power conversion process the small energy loss and hence high efficiency power conversion is important because of the extra cost of supplying lost energy and the difficulty to get rid of the generated heat by dissipation to air [3]. Although the cost of energy is subject of interest, the most unpleasant consequence of heat generation is that, it must be removed from the system. This consideration imposes the size and weight limits on the power electronic equipment [2].

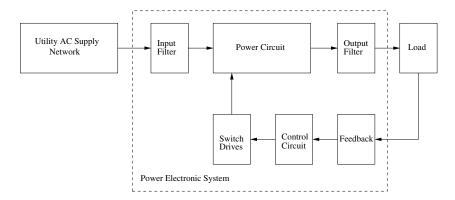

A power electronic system consists of much more than a power circuit. The block diagram of a typical system is shown in figure 1.1.

Figure 1.1: Block Diagram of Power Electronic System

Switching may create waveforms with harmonics that may be undesirable because they interfere with proper operation of the load or other equipment, so filters are often employed at the inputs and outputs of the power circuit. The system load which may be electrical or electromechanical is controlled via the feedback signal to the control circuit. The control circuit processes the feedback signal and drives the switches in the power circuit according to the demand of the load [2].

#### 1.1 Definitions

Some definitions widely used in power electronics are listed below

#### Peak

This is the maximum value attained by any waveform (voltage, current or power) [6].

#### Average

This is the DC component in the waveform and is described by the following equation for a periodic waveform v(t) of period T.

$$V_{av} = \frac{1}{T} \int_0^T v(t) dt \tag{1.1}$$

#### Root Mean Square (rms)

The rms value is the effective value of a waveform and relates to the power in the waveform. The rms value for a wave v(t) with a period of T is given by equation (1.2).

$$V_{rms} = \sqrt{\frac{1}{T} \int_0^T (v(t))^2 dt}$$

(1.2)

#### Ripple Factor

This is the ratio of the rms value to the absolute value of the DC component of a waveform [6].

$$r_f = \frac{\sqrt{(V_{rms}^2 - V_{av}^2)}}{V_{av}} \tag{1.3}$$

#### Form Factor

This is the ratio of the rms value to the average value of a waveform [6].

$$f_f = \frac{V_{rms}}{V_{av}} \tag{1.4}$$

#### **Crest Factor**

This is the ratio of the peak value to the rms value of a waveform [6].

$$c_f = \frac{V_{peak}}{V_{rms}} \tag{1.5}$$

#### Total Harmonic Distortion THD

It is normally defined for current and it is the ratio of the sum of the rms values of all harmonics components to the rms value of the current at the fundamental frequency [6].

$$THD = \frac{\sum I_{rms} Harmonics}{I_{rms} Fundamental}$$

(1.6)

#### Power

It is the rate of flow of the energy and normally refers to the average or real power. It can be defined for a given voltage v(t) and current i(t) as

$$P_{av} = \frac{1}{T} \int_0^T v(t) \cdot i(t) dt \tag{1.7}$$

#### Apparent Power or Volt-Amperes

This is the product of the rms voltage and the rms current [6].

$$P_{va} = V_{rms} \cdot I_{rms} \tag{1.8}$$

#### **Power Factor**

This is the ratio of the average power flowing to the load, to the apparent power in the circuit [6].

$$pf = \frac{P_{av}}{P_{va}} \tag{1.9}$$

#### Volt-Ampere Reactive

This is the power flowing into the reactive loads [6].

$$Q_{va} = \sqrt{P_{va}^2 - P_{av}^2} \tag{1.10}$$

#### Displacement Angle

This is the angle between the fundamental component of the input current and the input voltage [6]. It can be denoted by  $\phi_d$ .

#### **Displacement Factor**

This is the cosine of the displacement angle [6].

$$disp_f = cos(\phi_d) \tag{1.11}$$

#### **Distortion Factor**

This is the ratio of the power factor to the displacement factor [6].

$$dist_f = \frac{pf}{disp_f} \tag{1.12}$$

#### 1.2 Introduction to Rectifier Circuits

The rectifier circuit is the workhorse of the power electronic circuits, it links an AC supply to a DC load by converting an alternating voltage from the supply to a direct voltage to the load [7]. The obtained DC voltage is not normally level as from a battery, it contains an alternating ripple component imposed on the mean level [4]. The type of load connected to the rectifier terminals has an important effect on the behaviour of the circuit and on the imposed duty of the rectifier elements. For example, the load may be a pure resistive, capacitive or inductive, or it may consist of combination of resistance, inductance and capacitance. Each type of load provides different requirements in the application of the rectifier circuit. A study of the relations between the current and voltage waveforms in typical rectifier circuits with different loading conditions is demonstrated in many handbook of power electronics. This study leads to more understanding of the circuits behaviour [1,3,8].

Various circuit architectures are described in this section, although all give a DC output, but they differ in regards to the AC ripple at the output, the average voltage level, efficiency and their loading effects on the AC supply [2,4].

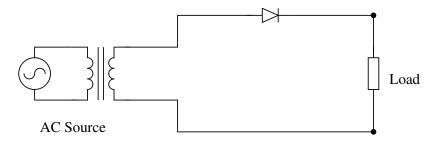

Rectifiers are usually considered in two groups, half-wave rectifiers where current is drawn from the supply during one half of the cycle and full-wave rectifiers where both positive and negative half cycles are utilised. The basic single phase half wave rectifier circuit is shown in figure 1.2.

Figure 1.2: A Single Phase Half-Wave Rectifier

However, except at very low power levels, half wave rectifiers are very rarely used [5]. This is to some extent because its output voltage contains ripple at the AC input frequency, which makes filtering more difficult than for other circuits having ripple frequen-

cies that are multiples of the input frequency, but more seriously, the DC load current flows in the secondary of the input transformer. Unless this transformer is designed to carry DC, which is unusual, this may cause saturation of the transformer core with associated power loss and distortion of the voltage waveform. Hence, half wave rectifier will be not considered any further [2, 5].

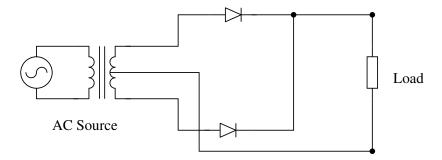

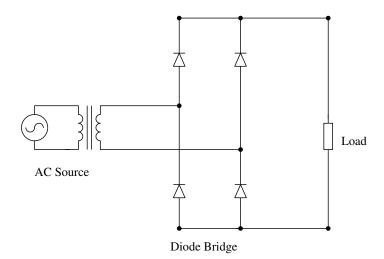

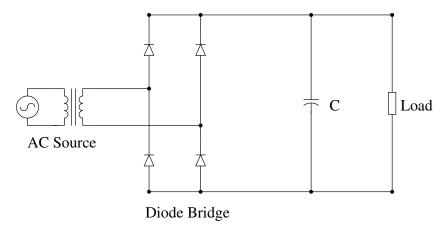

There are two basic full-wave rectifier circuits, the tapped transformer and the bridge rectifier [1]. The circuit diagram of both circuits are shown in figures 1.3 and 1.4 respectively.

Figure 1.3: A Single Phase Centre-Tapped Transformer Full-Wave Rectifier

Figure 1.4: A Single Phase Full-Wave Bridge Rectifier

The two circuits will produce the same voltage and current waveforms, but there are two differences. For the bridge rectifier circuit which is commonly used in industrial applications, the load current always flows through two diodes effectively in series.

The load voltage will therefore be less than the source voltage by the voltage lost across the two forward-biased diodes. The maximum inverse voltage applied to the

reverse biased diodes is the peak applied voltage [9]. This will reduce the efficiency particularly at low voltage purposes. The tapped transformer rectifier has only one diode carrying current during either half cycle, but the maximum reverse voltage across the reverse biased diode ( the diode not carrying current), will be a value of twice the peak load voltage [5]. The single phase full-wave rectifier with a sinusoidal voltage source will produce a load voltage like a train of positive sinusoidal half cycles waveform while what's required is a level voltage. To achieve this, the ripple energy must be stored in a filter between the rectifier and the load. This can be implemented by using an energy storage device which is often a capacitor. The circuit diagram of single phase full-wave bridge rectifier with a capacitor at the load side is shown in figure 1.5. The capacitor stores energy while the rectifier voltage is near its peak and then supplies the load current for the rest of the cycle. For this reason it is usually called a reservoir — capacitor.

Figure 1.5: A Single Phase Full-Wave Bridge Rectifier with Capacitor Filter

The simplicity in construction, low cost, and the reliability of this rectifier makes it widespread and widely used in domestic and industrial applications.

The main drawback of this design is the pulsating line current, which has a small duration, with a surge value. This current results in a large harmonics injected to the utility AC networks. The high content of harmonics in the line current of the rectifier is responsible for exposing the utility AC networks to a poor power factor and significant increase in losses and thus reduces the power networks efficiency.

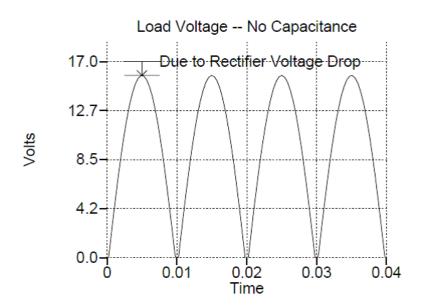

To clarify, the work of full-wave rectifier with capacitor filter, consider the following full-wave rectifier with an AC supply voltage of 220V and transformer winding ratio of

18: 1. The load voltage waveform for this rectifier without capacitor is shown in figures 1.6, while load voltage waveform with a capacitor is shown in figure 1.7.

Figure 1.6: Load Voltage without DC Side Capacitor

Figure 1.7: Load Voltage with DC Side Capacitor

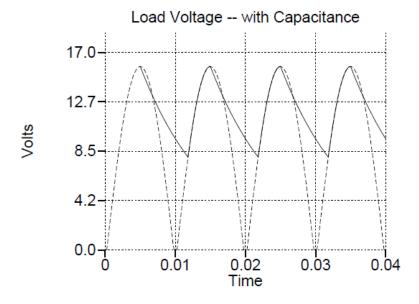

In order to calculate where the exponential waveform  $(Me^{-\frac{x}{\tau}})$  intersects the sinusoidal waveform with amplitude of M, the following equation needs to be solved. Where  $\tau = C \cdot R$  is the time constant of the CR network.

$$Me^{-\frac{x}{\tau}} = -M\cos(2\pi f x) \tag{1.13}$$

Or

$$e^{-\frac{x}{\tau}} + \cos(2\pi f x) = 0 \tag{1.14}$$

This equation can be sketched with an amplitude of M as shown in figure 1.8

Figure 1.8: Sketch of Equation (1.14)

Where,  $\alpha$  is normally specified as the conduction angle. In this figure,  $\alpha$  can be obtained from the location of intersect of two curves and then can be derived from x. However the solution of x results in the value of  $\alpha$  being in a time quantity ( $\alpha_{time}$ ), this can be converted eventually to an angle using the following relationships.

$$\alpha_{time} = x - \frac{1}{4f} \tag{1.15}$$

$$\alpha = \alpha_{time} 2\pi f \tag{1.16}$$

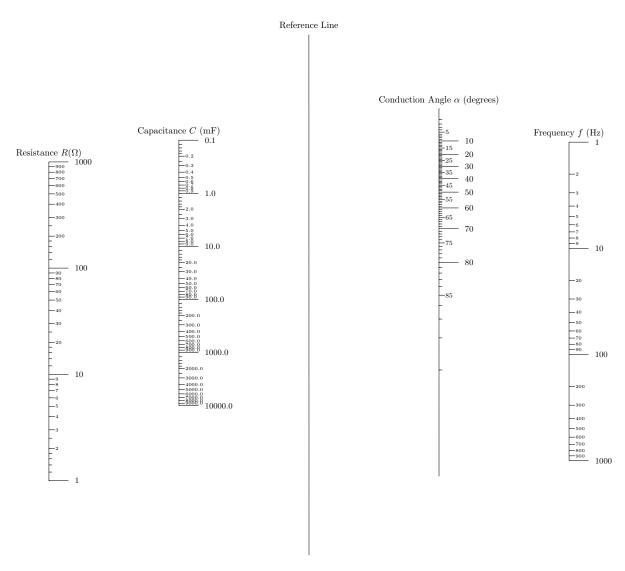

An analytical solution for equation (1.14) is done as a part of teaching [6] in Plymouth university is shown in figure 1.9.

Thus for a given C, R and f, the conduction angle  $\alpha$  can be derived. This conduction angle determines the average DC voltage across the load; the ripple and the input current.

Single-Phase Full-Wave Bridge Rectifier © University of Plymouth

Figure 1.9: Nomogram for Solving Equation (1.14)

The average value of the load voltage can be obtained from figure 1.8 and applying the definition of average which is given in equation (1.1). The exact solution can be obtained as follows

$$V_{average} = \frac{1}{Period} \int_{0}^{Period} v(t) dt$$

(1.17)

$$= \frac{1}{\frac{1}{2f}} \left[ \int_0^{\frac{\alpha}{4\pi f} + \frac{1}{4f}} Me^{-\frac{t}{\tau}} dt - \int_{\frac{\alpha}{4\pi f}}^{\frac{1}{2f}} M\cos(2\pi ft) dt \right]$$

(1.18)

$$= 2fM \left[ -\tau \left[ e^{-\frac{t}{\tau}} \right]_0^{\frac{\alpha}{4\pi f} + \frac{1}{4f}} - \frac{1}{2\pi f} \left[ sin(2\pi f t) \right]_{\frac{\alpha}{4\pi f} + \frac{1}{4f}}^{\frac{1}{2f}} \right]$$

(1.19)

$$V_{average} = M \left[ 2f\tau \left(1 - e^{-\left(\frac{\alpha}{4\pi f} + \frac{1}{4f}\right)/\tau}\right) + \frac{\cos(\alpha)}{\pi} \right]$$

(1.20)

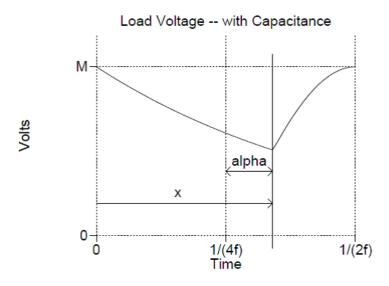

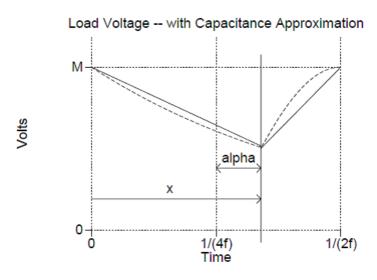

For most practical systems a straight line approximation is used to calculate the value of the average voltage. Figure 1.10 shows the sketch of equation (1.14) with straight line approximation.

Figure 1.10: Sketch of Equation (1.14) with Straight Line Approximation

This results in

$$V_{average} = \frac{1}{2}(M + Me^{-x/\tau}) \tag{1.21}$$

$$= \frac{M}{2}(1 + e^{-x/\tau}) \tag{1.22}$$

$$x = \frac{\alpha}{2\pi f} + \frac{1}{4f} \tag{1.23}$$

Or

$$V_{average} = \frac{1}{2}(M - M\cos(2\pi f x)) \tag{1.24}$$

$$= \frac{M}{2}(1+\sin(\alpha)) \tag{1.25}$$

For the above example, let  $\tau = 0.01s$ , f = 50Hz, M = 15.8V. For a given values of M, C, R and f, the value of  $\alpha$  can be determined and it was 30° in this case. Using the exact expression of  $V_{average}$  in (1.20), the value of the average voltage is found 12.01V, while with the approximation expression (1.25) is found  $V_{average} = 11.85V$ .

#### AC Side Current Analysis

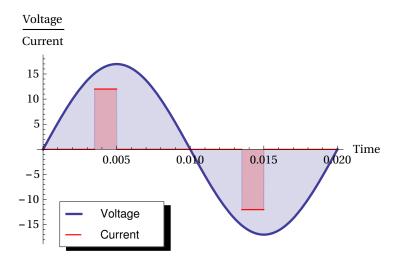

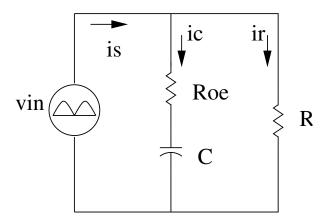

Once the diodes of the bridge rectifier start conducting, the mains current starts flowing in the circuit and the transformer output connected to the load via the DC side of the rectifier. For the case of pure resistive load connected to the bridge rectifier with a reservoir capacitor, this load actually consists of a resistor (load) in parallel with a capacitor (reservoir capacitor). Thus the current drawn from the transformer is given by (1.26).

$$i_{load} = \frac{M\cos(2\pi ft)}{Z_{load}} \tag{1.26}$$

$$Z_{load} = \frac{R_{j2\pi fC}^{-1}}{R + \frac{1}{j2\pi fC}} = \frac{R}{1 + j2\pi fCR}$$

(1.27)

The load current results in a complex quantity, this current waveform is normally approximated as a square waveform with an amplitude equal to the average of the wave described by equation (1.26).

The capacitor of capacitance C charging from  $V_{min} = MSin(\alpha)$  to  $V_{max} = M$ , results in a charge of  $C \cdot (V_{max} - V_{min})$ . The charge accumulated by the capacitor divided by the time it takes for the capacitor voltage to rise, gives the capacitor charge current. From figure 1.10, the time taken by the capacitor to charge  $t_c$  is given by (1.28).

$$t_c = \frac{1}{4f} - \frac{\alpha}{2\pi f} \tag{1.28}$$

Where,  $\alpha$  is in radians. If  $\alpha$  is in degree, then replace  $2\pi$  with 360.

Thus the capacitor charging current is approximately given by (1.29).

$$I_{charge} = \frac{C(V_{max} - V_{min})}{t_c} \tag{1.29}$$

The amplitude of the square current waveform is the sum of the capacitor charging current and the average load current.

Thus the amplitude of the square current waveform taken from the transformer  $(I_s)$  is given by the below expression.

$$I_s = \frac{C(V_{max} - V_{min})}{t_c} + \frac{V_{average}}{R} \tag{1.30}$$

$$I_{mains} = \frac{I_s}{N} \tag{1.31}$$

This equation is based on the straight line approximation of the charging phase. The current taken from the mains  $I_{mains}$  is a square waveform with peak amplitude smaller than the transformer current  $I_s$  by a factor equal to the transformer turns ratio N.

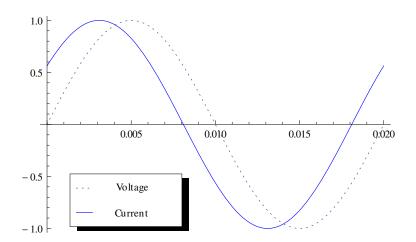

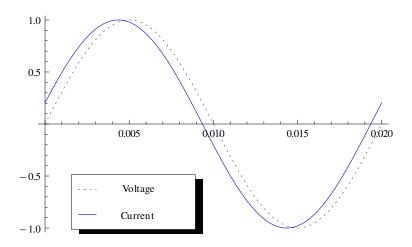

The generic waveforms of the supply voltage and the line current of the single phase rectifier system with a capacitor filter on the DC side are shown in figure 1.11.

Figure 1.11: Generic Supply Voltage and the Line Current Waveforms of the Single Phase Bridge Rectifier with Capacitor Filter

This current and through its surge value can result in a large amount of harmonics on the AC side of the rectifier and thus reducing the power networks capability to manage loads. It is likely, particularly for medium and high power applications, the summation of these surge currents (non-linear loads) for a specific load zone causes a system failure and service interruption due to the actions of protection circuits. This current also can lead to the unbalancing situation in three-phase systems, which is considered to be one of the most serious cases facing the power networks.

Harmonics are considered the source of many problems facing the safe and stable operation of the AC networks. They are responsible for a significant increase of losses in the transmission and distribution power networks due to the harmonic currents. Harmonic currents in this design can reach a considerable values from the fundamental component of the rectifier current (specifically for the low order harmonic components) and thus exposing the utility AC networks to low input power factor due to the large harmonic distortion.

Harmonics produce an EMI which is detrimental for the communications systems and radio signal control networks.

Harmonics play a key role in determining the validity of any system in terms of the harmonics content, and how much matching the harmonics content of any system to the standard harmonics restrictions at a certain power level. they are also specified in immunity standards and their reduction is a key to reduce noise in the power networks.

## 1.3 Introduction to Power Supplies

The simple rectifier circuits presented in section 1.2 are examples for unregulated power supplies. The load voltage will change in accordance to the changes in supply voltage or the load current. In order to stabilise the load voltage, another set of arrangement has to be added between the rectification stage and the load. The function of the new configuration is to keep the load voltage constant at a desired level with a small margin of voltage ripple across the load. Normally this task can be done either with a linear regulator or with a DC-DC converter depending on the kind of the application. In case of the linear regulator has been used then the power supply known as a linear power supply. When a DC-DC converter is used to regulate the voltage then the power supply known as switching power supply (or commonly known as switched-mode power supply). In both cases the function of the power supply is to convert an AC power to a DC power at a desired output level.

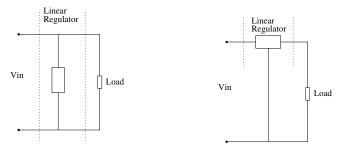

## 1.3.1 Linear Power Supplies

Linear power supplies consist of a rectifier and linear regulator. Linear regulator is an electronic regulator in which the voltage or current is controlled using transistors and other active devices as variable impedance elements. Usually regulators are designed to provide a constant load voltage as this is required for most electronic equipment. Regulators may also be used to stabilize the current where this is required by the load [5].

Regulators can be divided into two groups, shunt and series. The shunt regulator has a variable impedance element in parallel with the load. The circuit diagram of the shunt regulator is shown in 1.12. The element diverts current from the load and the load

voltage then can be controlled by varying the amount of the diverted current. The series regulator has a variable impedance element connected in series between the supply and the load. The circuit diagram of the series regulator is shown in 1.13. The voltage across the load is sensed and the impedance of the series element varied in accordance to keep the load voltage constant.

Figure 1.12: Shunt Regulator

Figure 1.13: Series Regulator

This kind of power supplies provide only a step-down DC voltage from the average input voltage. There is always a voltage drop across the linear regulator and a power loss associated with this voltage drop. The loss of energy in the regulator becomes very significant when a lot of current is drawn from the power supply and thus the switching power supply becomes the better choice [6].

Linear supplies have the following advantages over switching power supplies [10].

- Linear supplies provide a smoother output and they are cheap for low power applications.

- Simpler in design and circuit complexity is low.

- Linear supplies are produce less electrical and electromagnetic interferences, as there is no high frequency switching noise or EMI.

However, except where power is low and efficiency is not important, or where low rate of noise and high stability are required, there is limited use of these kind of power supplies.

### 1.3.2 Switching Mode Power Supplies

Switching power supplies consist of a rectifier and a DC-DC converter. The input into the DC-DC converter is an unregulated DC power which is the output of the rectifier circuit. The function of the converter is to convert the unregulated DC input into a regulated DC output at a desired output level [3].

DC-DC converters utilize one or more switches to transform DC voltage from one level to another and they are more efficient compared to the linear regulators. They are observing the voltage at the load side and switch in the rectifier if the voltage drops below a lower threshold and switch out the rectifier when the voltage exceeds an upper threshold [6]. They can provide outputs which they are equal to; lower than; higher than or with reversed polarity to the inputs [11]. These converters have many circuit configurations and thus it is not possible to consider all of these circuits in this section. There are three basic types of converters, step-down mode (buck); step-up mode (boost) and the step-up-down mode (buck-boost). They differ in the way that the magnetic elements are operated and each of them has its own unique features.

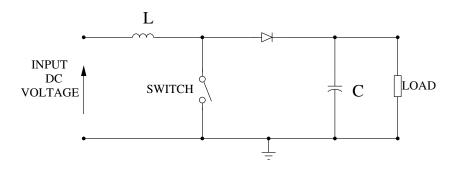

### Step-Down or Buck Converter

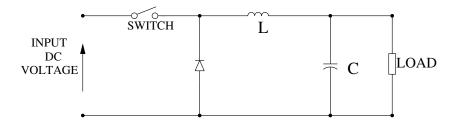

As the name implies, a step-down converter produces a lower average output voltage than the average input voltage [3]. The circuit configuration of the step-down converter is shown in figure 1.14.

Figure 1.14: Step-Down or Buck Converter

The series switch S is turned on and off within a switching period of T and duty ratio of D. The free-wheeling diode provides an alternative path for the current in the inductor L when the switch is turned off. The capacitor C across the load ensures that the load

voltage is relatively constant [5]. In order to clarify the operation of this converter, the following assumptions have been made

- 1. The input voltage is always higher the output voltage  $(V_{in} > V_{out})$ , and  $V_{in}$  is the average rectified voltage.

- 2. The output voltage  $V_{out}$  is not isolated from the input voltage  $V_{in}$ .

- 3. The inductor current does not fall to zero (the operation of the converter is in CCM only).

- 4. The magnetic field in the inductor does not saturate.

- 5. The capacitor current rises and falls in order to balance the difference between the inductor current and the load current.

The principle of operation of the buck converter can be divided into two states with two periods.

These periods can be defined as  $t_{on}$  when the switch is turned on and  $t_{off}$  when the switch is off. The sum of these two periods referred to the switching period T. Then the duty cycle (D) of the switch which controls the average output voltage can be defined as

$$T = t_{on} + t_{off} (1.32)$$

$$D = \frac{t_{on}}{T} \tag{1.33}$$

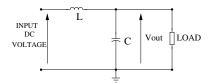

### • On State $(0 < t \le t_{on})$

This state begins when the switch is turned on at t = 0. The input current with ascending tendency flows through the inductor L and supplies the load and the capacitor C. During this period, the energy is stored as an increase in the magnetic field of the inductor L. The capacitor C cannot store the energy as the output voltage is relatively constant.

Since the switch S is turned off for a very short time, then the input voltage can be assumed as a DC voltage of value  $V_{in}$ , while the output voltage across the load can be denoted as  $V_{out}$ . The voltage and current through the inductor L are related by the following equation

$$V_{inductor} = L \frac{di}{dt} \tag{1.34}$$

This means that,

$$V_{in} - V_{out} = L\frac{di}{dt} \tag{1.35}$$

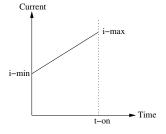

The inductor current changes from  $i_{min}$  to  $i_{max}$  in the time period from t = 0 to  $t = t_{on}$  and then the differential equation of (1.35) can be replaced with an approximation as follows:

$$V_{in} - V_{out} = L \frac{(i_{max} - i_{min})}{t_{om}}$$

(1.36)

This results in

$$(i_{max} - i_{min}) = \frac{(V_{in} - V_{out})}{L} t_{on}$$

(1.37)

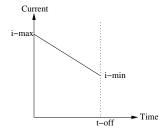

## • Off State $(t_{on} < t \le (T - t_{on}))$

When the switch is turned off, the voltage at the input of the inductor L tries to fall below zero (very large reverse voltage is induced in order to keep the current flow) and as a consequences of that, the diode is turned on and the input voltage of the inductor is connected to ground assuming the voltage drop across the forward biased diode is zero. This leads to the output voltage of the inductor L is  $V_{out}$  and the inductor current decreases from its value of  $i_{max}$  to  $i_{min}$  at the end of  $t_{off}$ .

$$-V_{out} = L \frac{(i_{min} - i_{max})}{t_{off}} \tag{1.38}$$

$$(i_{max} - i_{min}) = \frac{V_{out}}{L} t_{off}$$

(1.39)

For CCM of operation and at steady state conditions, the rise in inductor current during the on state should equal to the fall in current during the off state. From (1.37) and (1.39) can get

$$\frac{(V_{in} - V_{out})}{L} t_{on} = \frac{V_{out}}{L} t_{off}$$

(1.40)

This results in

$$V_{out} = \frac{t_{on}}{(t_{on} + t_{off})} V_{in} = D V_{in}$$

(1.41)

L Vout LOAD

Figure 1.15: On State Circuit Diagram

Figure 1.16: Off State Circuit Diagram

Figure 1.17: Inductor Current at On State

Figure 1.18: Inductor Current at Off State

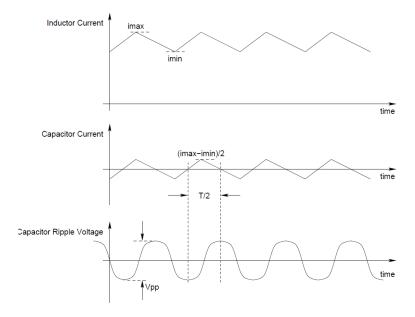

The ripple voltage can be determined by assuming the load current is constant and the variation in the inductor current is balanced by the capacitor. The ripple voltage can be obtained using the relationship between the voltage across the capacitor  $V_{PP}$

and the capacitor current  $i_c$ . Where,  $V_{pp}$  is the peak to peak ripple voltage across the capacitor [6].

$$i_c = C \frac{dV_{pp}}{dt} (1.42)$$

$$V_{pp} = \frac{1}{C} \int i_c dt \tag{1.43}$$

The peak of the capacitor current  $i_{cmax}$  is the average of the of the inductor current.

$$i_{cmax} = \frac{(i_{max} - i_{min})}{2} \tag{1.44}$$

By the substitution in equations (1.32), (1.33) and (1.39), results

$$i_{cmax} = \frac{1}{2} \frac{V_{out}}{L} (1 - D) T$$

(1.45)

The approximate capacitor ripple voltage and current with the inductor current are all shown in figure 1.19.

Figure 1.19: An Approximate Capacitor Ripple Voltage and Current with the Inductor Current

The integral of the current waveform (the area under the curve) is the area of a triangle with base of T/2 and height of  $i_{cmax}$ .

$$V_{pp} = \frac{1}{C} \cdot \frac{1}{2} \cdot \frac{T}{2} \cdot i_{cmax} \tag{1.46}$$

$$= \frac{1}{4C} \cdot \frac{V_{out}}{2L} \cdot (1-D) T^2 \tag{1.47}$$

$$= \frac{1}{8} \cdot \frac{1}{LC} \cdot V_{out} (1 - D) T^2$$

(1.48)

$$= V_{out} \cdot \frac{(1-D)}{8LC} T^2 \tag{1.49}$$

Using the following definitions

$$f_s = \frac{1}{T} \tag{1.50}$$

$$f_c = \frac{1}{2\pi\sqrt{LC}} \tag{1.51}$$

Where,  $f_s$  is the switching frequency,  $f_c$  is the cut-off frequency of the chosen values of L and C.

$$V_{pp} = V_{out} (1 - D) \frac{\pi^2}{2} \left(\frac{f_c}{f_s}\right)^2$$

(1.52)

From (1.52), it is clear that the load voltage ripple is independent of the load current and it is determined by the output voltage; duty cycle; switching frequency and the chosen values of L and C.

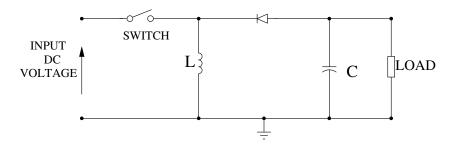

#### Boost Mode or Step-Up Converter

It is clear from the name of this converter, the output voltage is always higher than the average input voltage [1].

The circuit configuration of the step-up converter is shown in figure 1.20.

The operation of this converter can be also divided into two states (on and off state). When the switch is closed (on state), the diode is being reversed biased and the load is supplied completely from the capacitor. The current in the inductor increases and thus the stored energy in the inductor is increased. When the switch is opened (off state), the load receives the energy from the inductor and as well as from the supply [12].

Figure 1.20: Step-Up or Boost Converter

Using similar way of analysis as in the buck converter, the output voltage can be obtained as follows

$$V_{out} = \frac{1}{(1-D)} V_{in} {1.53}$$

Where, D is the duty cycle of the switch.

The output voltage ripple can be determined by computing the voltage drop of the CR network when the switch is on. This is identical to the set-up described in section 1.2. The following assumption can be made [6].

$$V_{out} \approx V_{max} e^{-\frac{t_{on}}{CR}} \tag{1.54}$$

$$V_{min} = V_{max} e^{-\frac{t_{on}}{CR}} \tag{1.55}$$

$$V_{pp} = V_{max} - V_{min} (1.56)$$

$$V_{pp} = V_{out} \frac{(1 - e^{-\frac{t_{on}}{CR}})}{e^{-\frac{t_{on}}{2CR}}}$$

(1.57)

Under the assumption  $t_{on} \ll CR$ , and using the mathematical series expansion of the exponential function, the final expression of the peak to peak ripple voltage  $V_{pp}$  can be found as

$$V_{pp} \approx V_{out} \frac{t_{on}}{CR} \tag{1.58}$$

#### Buck-Boost or Step-Up-Down Converter

The third type of the basic converter circuits is the buck-boost circuit. The main application of this kind of converter is where a negative polarity output may be desired with respect to the common terminal of the input voltage. The output voltage can be either higher or lower than the input voltage [3]. The circuit configuration is show in figure 1.21.

Figure 1.21: Step-Up-Down Converter

In this converter, while the switch is turned on, the inductor current increases and the energy is being stored in the inductor until the switch is turned off. When the switch is turned off, the voltage across the inductor is reversed and the current in the inductor continues to flow. As a results of that the diode being forward biased and the the inductor current is transferred to the load [5]. Using similar way of analysis as in the buck and boost converters, the output voltage can be obtained as follows

$$V_{out} = \frac{D}{(1-D)} V_{in} {1.59}$$

Where, D is the duty cycle of the switch.

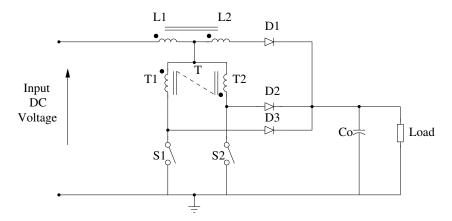

### Weinberg Boost Converter

Weinberg topology was invented in 1974. This boost converter is configured as a high power and high efficiency for space applications [13]. It was designed essentially for satellite power systems when battery power storage is required to supply a regulated mains voltage. The circuit configuration of Weinberg converter is shown in figure 1.22.

Figure 1.22: Weinberg Converter

Weinberg converter utilises the close-coupled inductors topology with a main inductor which is divided into two identical parts before and after the common point of the closed coupled inductors. This converter is designed to ensure a continuous output current by providing an alternative (parallel) path for energy to flow into the load side. The principle of operation of this converter has two states:

- $S_1$  or  $S_2$  switched On, forcing  $D_2$  or  $D_3$  respectively to be also On, while  $D_1$  is Off.

- $S_1$  and  $S_2$  switched both Off, and  $D_1$  is On.

By control the operation of switches  $S_1$  and  $S_2$ , the output voltage of the converter can be controlled. The output voltage of Weinberg converter can be expressed as in (1.60).

$$V_{out} = (1+D) \ V_{in} \tag{1.60}$$

Where, D is the duty cycle of switches  $S_1$  and  $S_2$ .

It is clear that the output voltage can reach any possible value between the input voltage and twice the input voltage. This converter showed a reasonable performance with respect to efficiency; reduced mass and power handling capability. A superior power density with a high efficiency of more than 97% on the 100~kW class close-coupled converter is demonstrated in [14].

## 1.4 Thesis Aims and Organisation

This thesis investigates the A.C to D.C power conversion in single phase systems. The research consists mainly of two phases. The first phase is focused on the investigations to find a new approach of rectification in single phase systems. A novel single phase rectification technique with a new architecture and control strategy is proposed. The new technique aims to increase the low input power factor in the conventional single phase rectifier system (typically between 0.3-0.6) and thus higher efficiency can be achieved. The new rectifier architecture also aims to provide a reduction in the size of the DC side capacitor which results in lower content of harmonic in the rectifier line current. The presence of the large smoothing capacitor in the conventional rectifier system results in the generation of a considerable line current harmonics to be injected into the utility AC supply networks.

The second phase of this research is focused on the DC-DC conversion. A novel buck-boost DC-DC converter architecture using close-coupled inductors with its transfer function is proposed. The new topology aims to reduce the switching noise and thus the switching losses that usually accompanies the conventional buck and boost converter circuits. The reduction in the system losses leads to higher power conversion efficiency for this kind of converters dealing with a wide range of supply voltages and serves a wide variety of applications.

This thesis is organised into five chapters as follows: Chapter 2, is the literature review of research in AC-DC power conversion for single phase systems. This literature review has been classified into two parts. The first part is interested in research which is

concerned with the new rectification techniques and methods to improve the performance of the conventional single phase rectifier system. The second part of the literature review is focused on research which is concerned with the new DC-DC conversion architectures.

Chapter 3, presented a novel single phase rectification technique with a new architecture and control strategy. The circuit configuration of the new rectifier and the principles of operation are presented. The AC side analysis of the rectifier line current is done using Woodward's notations applied to chopped waveforms. The prototype circuits of the proposed and the conventional single phase rectifiers have been designed, fabricated and tested. A comparison between the performances of the two rectifiers by conducting two case studies has been done. The performance analysis of the proposed rectification technique is demonstrated with a wide range of case studies and different sets of design parameters have been undertaken.

In chapter 4, a novel buck-boost DC-DC converter architecture with its transfer function is presented. The circuit configuration of the proposed converter and the principles of operation are presented. This converter utilises the close inversely-coupled inductors topology in both its conversion stages (buck and boost). The transfer function of the buck-boost converter in CCM of operation and steady state conditions is given. The prototype circuit of the proposed converter has been fabricated and tested. The practical results of a range of case studies are included in this work. A simulation model for the converter circuit is also done using LT spice IV4.22. The simulation model has been examined with the same case studies that been conducted in the practical part.

In Chapter 5, the work presented in this thesis is concluded and some suggestions for future work in this area are given.

## 1.5 Contribution to Knowledge

The following list summarises the main contributions of the dissertation.

• A novel single phase rectification technique with a new architecture and control scheme.

The new rectifier allows to obtain high input power factor and thus higher efficiency to be achieved. The current harmonics generation in the proposed technique can be suppressed which results in lower content of harmonic in the line current of the rectifier. Woodward's notation is used in the AC side analysis of the proposed and the conventional rectifiers, which is considered a new method of signal analysing in this field. The rectifier architecture provides a reduction in the size of the DC side capacitor. This reduction can be as low as less than 10% of the size of the typical smoothing capacitor in the conventional single phase rectifier. The size of smoothing capacitor restricts the power density of the conventional system. The new rectifier now allows the possibility to increase the power rating of such rectifiers to a higher values. This contribution is presented by the author and published in:

- S. Al-Zubaidi; M.Z.Ahmed; P.Davey, "Design of Single Bidirectional Switch Single Phase Rectifier with Reduced Size DC Side Capacitor," IEEE Conference, The First International Future Energy Electronics Conference (IFEEC), Tainan, Taiwan, Nov. 2013.

- S. Al-Zubaidi; M.Z.Ahmed; P.Davey, "High Power Factor Single Phase Rectification Technique with Reduced Line Current Harmonics," IEEE Workshop, The Fifteenth IEEE Workshop on Control and Modelling for Power Electronics (COMPEL), Santander, Spain, June 2014.

This contribution also has been published in:

WIPO - World Intellectual Property Organization, Publication No.: WO/2015/008039, Publication Date: 22.01.2015.

• A novel buck-boost DC-DC converter architecture using close-coupled inductors with its transfer function.

Converters utilise the coupled inductor topology can achieve a higher power densities with better performance. The new converter architecture strongly reduces the switching noise and thus reduces the switching losses that usually accompanies the conventional converter circuits. Switching noise is considered as a major drawback in the typical buck and boost converter circuits which causes a significant switching losses and results in high voltage stress on the power switches.

The new architecture ensures the maintaining of continuous flow of current in both converter stages (buck and boost), which results in large reduction in the back e.m.f induced in the main inductor and thus reduces the switching noise. As a consequences of that higher power conversion efficiency with less switching noise can be achieved with the proposed converter.

The new converter architecture also provides a unique design of the passive clamped circuit. The function of the proposed clamped circuit is to recycle the leakage energies of the coupled inductors which results in an efficiency improvement of the power conversion process. Also, this circuit is used to clamp the large voltage spikes (due to the impedance buffer provided by the coupled inductors) in order to limit the voltage stress on the power switches.

This contribution is presented by the author and published in:

S. Al-Zubaidi; M.Z.Ahmed; P.Davey, "A Novel Buck-Boost DC-DC Converter Using Close-Coupled Inductors," IEEE Symposium,

The Sixth International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aachen, Germany, June 2015.

# Chapter 2

# Literature Review

## 2.1 Single Phase Rectifier

The enormous increase in non-linear loads connected to the utility AC supply represent a serious challenge because of the pulsating current. This current has a small duration with a surge value can result in large harmonics injected to the utility AC supply. The high content of harmonic currents in the AC side of these non-linear loads is responsible for exposing the utility AC networks to poor power factor and a significant increase in losses and thus reduces the power networks efficiency. The harmonic currents produced by non-linear loads tends to produce a voltage harmonics to the mains. These voltage harmonics or voltage distortion in the mains, have an effect on the harmonic characteristics of the input current are dependent not only on the magnitude of the supply voltage harmonics but also on their phase angles [15].

The reason behind this current harmonic phenomenon is the large smoothing capacitor (reservoir capacitor) required to reduce the ripple power in the DC side of the rectifier. The size of this capacitor restricts the capability of increasing the power density of such loads.

From the above it seems that there is a need for a new rectification technique for single phase system. This technique should meet the following fundamental requirements:

1. High input power factor with low harmonic content in the line current of the rectifier.

- 2. Simplicity and reliability with low component count.

- 3. The capability of increasing power density and simple control scheme.

High input power factor with reduced line current harmonics ensures a significant reduction in the total system losses and provides an efficient, safe and reliable operation of the utility AC supply networks.

Simplicity in design and control scheme of any proposed architecture enables increasing the power density and provides a high level of reliability for the system which makes it popular for a wide variety of applications.

One of the widely used non linear load is the single phase bridge rectifier with a DC side capacitor. Figure 2.1 shows the circuit configuration of the conventional single phase rectifier identifying the regions of interest for research.

Figure 2.1: Single Phase Bridge Rectifier with Marked Regions of Research Groups

A literature in this field can be classified in general into two main groups:

- 1. Research focus on the AC side of the rectifier (including the diode bridge).

- 2. Research focus on the DC side of the rectifier (including the diode bridge).

Research has identified different ideas to improve the power factor; efficiency and reduce the harmonics content of the line current of conventional rectifier. A brief survey of research in this field is presented as follows:

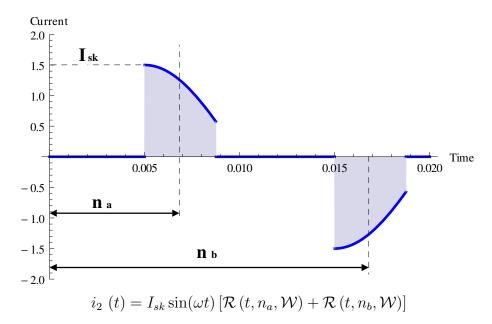

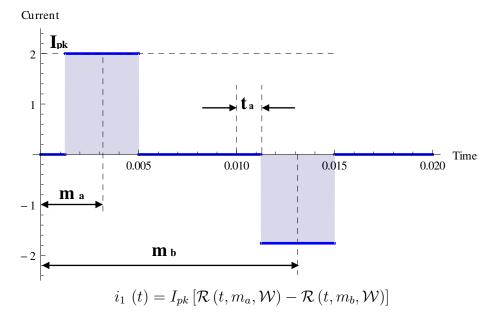

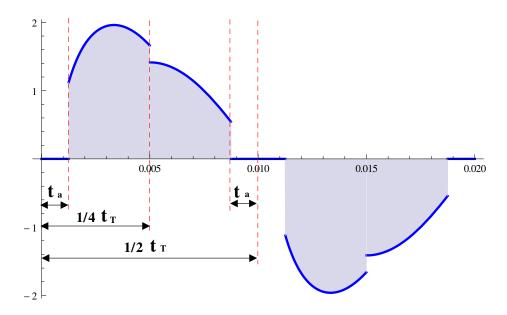

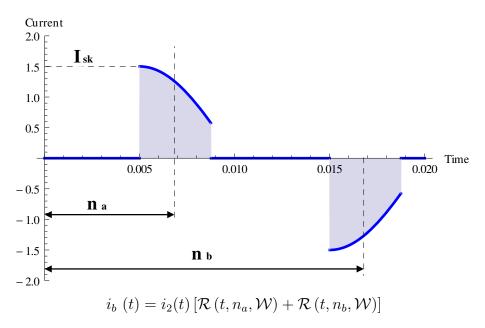

### 2.1.1 Research in the AC Side of Rectifier