04 University of Plymouth Research Theses

https://pearl.plymouth.ac.uk

01 Research Theses Main Collection

2013

# ON REDUCING THE DECODING COMPLEXITY OF SHINGLED MAGNETIC RECORDING SYSTEM

## Awad, Nadia

http://hdl.handle.net/10026.1/1594

http://dx.doi.org/10.24382/4719 University of Plymouth

All content in PEARL is protected by copyright law. Author manuscripts are made available in accordance with publisher policies. Please cite only the published version using the details provided on the item record or document. In the absence of an open licence (e.g. Creative Commons), permissions for further reuse of content should be sought from the publisher or author.

## ON REDUCING THE DECODING COMPLEXITY OF SHINGLED MAGNETIC RECORDING SYSTEM

by

Nadia Awad

Ph.D.

May 2013

Copyright ©2013 Nadia Awad

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without authors prior consent.

## ON REDUCING THE DECODING COMPLEXITY OF SHINGLED MAGNETIC RECORDING SYSTEM

A thesis submitted to Plymouth University in partial fulfillment of the requirements for the degree of

## **Doctor of Philosophy**

## Nadia Awad

May 2013

School of Computing and Mathematics Faculty of Science and Technology Plymouth University, UK

## Abstract

### **On Reducing the Decoding Complexity of Shingled**

### Magnetic Recording System

### Nadia Awad

Shingled Magnetic Recording (SMR) has been recognised as one of the alternative technologies to achieve an areal density beyond the limit of the perpendicular recording technique, 1 Tb/in<sup>2</sup>, which has an advantage of extending the use of the conventional method media and read/write head.

This work presents SMR system subject to both Inter Symbol Interference (ISI) and Inter Track Interference (ITI) and investigates different equalisation/detection techniques in order to reduce the complexity of this system.

To investigate the ITI in shingled systems, one-track one-head system model has been extended into two-track one-head system model to have two interfering tracks. Consequently, six novel decoding techniques have been applied to the new system in order to find the Maximum Likelihood (ML) sequence. The decoding complexity of the six techniques has been investigated and then measured. The results show that the complexity is reduced by more than three times with 0.5 dB loss in performance.

To measure this complexity practically, perpendicular recording system has been implemented in hardware. Hardware architectures are designed for that system with successful Quartus II fitter which are: Perpendicular Magnetic Recording (PMR) channel, digital filter equaliser with and without Additive White Gaussian Noise (AWGN) and ideal channel architectures. Two different hardware designs are implemented for Viterbi Algorithm (VA), however, Quartus II fitter for both of them was unsuccessful. It is found that, Simulink/Digital Signal Processing (DSP) Builder based designs are not efficient for complex algorithms and the eligible solution for such designs is writing Hardware Description Language (HDL) codes for those algorithms. To my beloved

Mother

and

sister; Fatin

for their support, encouragement and constant love

## Acknowledgments

First and foremost, praises and thanks to Allah, the Almighty, for His showers of blessings throughout my research work.

I would like to express my deepest appreciation to all those who helped and supported me in my research.

I will always be in debt to my first supervisor Mohammed Zaki Ahmed for his excellent guidance, encouragement, full support, deep intuition, and constant help throughout my research. His mark in my PhD time and in my life will never be forgotten.

My second supervisor, Paul Davey, thanks a lot for the useful discussions which have broadened my knowledge. Professor Martin Tomlinson, much appreciated your support.

My deepest thanks and gratitude extend to Dr. Mustafa M. Aziz at Exeter University who introduced me to my supervisor Zaki without whom I would not achieve what I achieved now.

I would also like to thank the Ministry of Higher Education and Scientific Research in Iraq for the financial support.

I would also like to offer my sincere thanks to all my colleagues in Smeaton 208 for their support. My colleague, Is-Haka Mkwawa, thanks a lot for your help on Latex, support, proof-reading my thesis and various discussions. You are always willing to help and give the best suggestions and solutions. My greatest thanks must go to all Iraqi's friends and colleagues at Plymouth University especially Samahir, Hanady, Haseba, Ali Al-Timemy, Saif, Salah and Adhraa for their help and support which made my time in Plymouth so enjoyable.

Lastly, I would like to thank my family for all their love and moral support and sacrifices. My mother, brother and sisters have given so much to bring me up. You are the people who have made me who I am and I would be nothing without you. I love you more than you can imagine.

# **Author's Declaration**

At no time during the registration for the degree of Doctor of Philosophy has the author been registered for any other University award without prior agreement of the Graduate Committee.

This study was financed under the Ministry of Higher Education and Scientific Research in Iraq scholarship for "Data Communications".

A programme of advanced study was undertaken, which included the extensive reading of literature relevant to the research project, development of softwares based simulations, development of practical designs and attendance of international conferences on magnetic recording area.

The author has submitted papers at The 2012 IEEE Intermag Conference at Vancouver, Canada, The 2013 IEEE Joint MMM Intermag Conference at Colorado, USA and The 2013 3rd International Symposium on Advanced Magnetic Materials and Applications. In addition the author attended The 2011 IEEE Intermag Conference at Taipei, Taiwan.

Word count of main body of thesis: 41004

Signed.....

Date.....

# Contents

| Abstrac             | t                                                           | i   |

|---------------------|-------------------------------------------------------------|-----|

| Acknow              | vledgments                                                  | iii |

| Author <sup>9</sup> | s Declaration                                               | v   |

| Conten              | ts                                                          | vi  |

| List of [           | fables                                                      | ix  |

| List of l           | igures                                                      | X   |

| Chapte              | r1: Introduction                                            | 4   |

| 1.1                 | History of Hard Disk Drive                                  | 5   |

| 1.2                 | Communication Channel for Magnetic Storage                  | 7   |

| 1.3                 | Data Storage Devices                                        | 8   |

| 1.4                 | Hard Disk Drive Components                                  | 9   |

| 1.5                 | Longitudinal Recording Technology                           | 11  |

| 1.6                 | Perpendicular Recording Technology                          | 13  |

|                     | 1.6.1 <b>PMR Advantages Over LMR</b>                        | 14  |

| 1.7                 | Future Technology Options                                   | 16  |

| 1.8                 | Shingled Writing Technology                                 | 19  |

| 1.9                 | Aim and Objectives                                          | 20  |

|                     | Contributions to Knowledge                                  | 22  |

|                     | Thesis Structure                                            | 24  |

| Chapte              |                                                             | 27  |

| 2.1                 | Introduction                                                | 27  |

| 2.2                 | Data Storage Channel Model                                  | 27  |

|                     | 2.2.1 Longitudinal Magnetic Recording Channel Model         | 28  |

|                     | 2.2.2 <b>Perpendicular Magnetic Recording Channel Model</b> | 32  |

| 2.3                 | PRML Method                                                 | 33  |

|                     | 2.3.1 Partial Response Equalisation                         | 37  |

|                     | 2.3.2 PRML Target Selection                                 | 39  |

|        | 2.3.3 Maximum Likelihood Sequence Detector Method  | 42  |

|--------|----------------------------------------------------|-----|

| 2.4    | Detection Algorithms                               | 44  |

|        | 2.4.1 Viterbi Algorithm                            | 44  |

|        | 2.4.2 <b>MAP Algorithm</b>                         | 45  |

| 2.5    | Readback Process of Perpendicular Recording System | 45  |

| 2.6    | Summary                                            | 46  |

| Chapte | r3: Implementation of PRML Channel                 | 48  |

| 3.1    | Introduction                                       | 48  |

| 3.2    | Simulation of Perpendicular Recording Channel      | 48  |

| 3.3    | Implementation of the Digital Equaliser            |     |

| 3.4    | Frequency Response of the Ideal Channel            | 53  |

| 3.5    | SNR Definition in Magnetic Recording Systems       | 56  |

| 3.6    | Standard Normal Distribution                       | 59  |

|        | 3.6.1 Memoryless Channel                           | 60  |

| 3.7    | MLSD Decoder                                       | 63  |

|        | 3.7.1 Implementation of MLSD                       | 63  |

| 3.8    | Implementation of the Viterbi Detector             | 67  |

|        | 3.8.1 Modification of Viterbi Algorithm            | 67  |

| 3.9    | Implementation of MAP Algorithm                    | 68  |

|        | 3.9.1 MAP Implementation: An Example               | 69  |

|        | 3.9.2 Modification of MAP Algorithm                | 75  |

| 3.10   | Simulation Results and Discussion                  | 76  |

|        | 3.10.1 Distance Metrics Graphs                     | 76  |

|        | 3.10.2 <b>PRML System Performance</b>              | 80  |

|        | 3.10.3 <b>Effective SNR</b>                        | 83  |

| 3.11   | Summary                                            | 84  |

| Chapte | r4: Shingled System Implementation                 | 86  |

| 4.1    | Introduction                                       | 86  |

| 4.2    | Complexity                                         | 87  |

| 4.3    | What is ITI?                                       | 88  |

| 4.4    | Implementation of Shingled System                  | 91  |

|        | 4.4.1 <b>2-D Equaliser Implementation</b>          | 92  |

|        | 4.4.2 <b>2-D Detection</b>                         | 93  |

| 4.5    | Decoding Techniques                                | 97  |

| 4.6    | Finding the Complexity of the Decoding Techniques  | 99  |

| 4.7    | ITI System Performance Discussion                  | 101 |

| 4.8    | Performance Evaluation                             | 110 |

| 4.9    | Summary                                            | 117 |

|        |                                                    | 110 |

## Chapter5:Introduction to FPGA Design Implementation118

| 5.1     | Introduction                                                       | . 118 |

|---------|--------------------------------------------------------------------|-------|

| 5.2     | FPGAs and DSP Processors                                           | . 118 |

| 5.3     | STM32F4 High-Performance Discovery Board                           | . 122 |

| 5.4     | DSP Builder Software                                               | . 122 |

| 5.5     | ModelSim Software                                                  | . 124 |

| 5.6     | Altera Quartus II Software                                         | . 124 |

| 5.7     | What is an FPGA?                                                   | . 125 |

| 5.8     | How to Create an Altera FPGA Design?                               | . 126 |

|         | 5.8.1 Schematic Diagram                                            | . 127 |

|         | 5.8.2 <b>VHDL</b>                                                  | . 127 |

| 5.9     | Implementation a Model (Block diagram) in Hardware                 | . 128 |

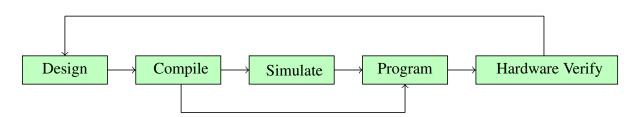

|         | 5.9.1 <b>Design Flow of Simulink Models</b>                        | . 128 |

|         | 5.9.2 Quartus II Implementation of Schematic Diagram and VHDL      |       |

|         | Designs                                                            | . 131 |

|         | 5.9.3 Adding a Design into Quartus II Environment                  | . 131 |

| 5.10    | Summary                                                            | . 134 |

| Chapte  | r6: Hardware Implementation of PRML System                         | 135   |

| 6.1     | Introduction                                                       | . 135 |

| 6.2     | Hardware Implementation of PRML Block Diagram                      | . 136 |

| 6.3     | Hardware Implementation of PMR Channel                             |       |

|         | 6.3.1 Simulink/DSP Builder Softwares Implementation of PMR Chan-   |       |

|         | nel                                                                |       |

|         | 6.3.2 Verifying Channel Simulink Design in ModelSim Software       | . 145 |

|         | 6.3.3 Verifying Channel Simulink Design in Hardware                |       |

| 6.4     | Hardware Implementation of PR Equaliser                            |       |

|         | 6.4.1 Simulink/DSP Builder Softwares Implementation of PR Equalise |       |

|         | 6.4.2 Verifying Equaliser Simulink Design in Hardware              |       |

|         | 6.4.3 Running Equaliser Design in FPGA Chip                        |       |

| 6.5     | Hardware Implementation of Viterbi Algorithm                       |       |

|         | 6.5.1 Simulink/DSP Builder Implementation of VA                    |       |

|         | 6.5.2 Verifying VA Simulink Design in Hardware                     |       |

| 6.6     | Summary                                                            |       |

| Chapte  | r7: Conclusions and Future Work                                    | 179   |

| 7.1     | Conclusions                                                        |       |

| 7.2     | Future Work                                                        |       |

| Bibliog | raphy                                                              | 187   |

| -~8     |                                                                    | -07   |

# **List of Tables**

| 2.1                                           | Partial-Response Channels                                                                                                                                       | 39                       |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 2.2                                           | The Popular PR Channels Used in Magnetic Recording                                                                                                              | 40                       |

| 2.3                                           | PRML Channels for Perpendicular and Longitudinal Magnetic Recording .                                                                                           | 42                       |

| 3.1                                           | States Table of The Ideal Channel                                                                                                                               | 52                       |

| 3.2                                           | Noise Power Values for Different Values of SNR in dB                                                                                                            | 58                       |

| 3.3                                           | The pdfs of The Ideal Output Samples                                                                                                                            | 66                       |

| 3.4                                           | VA Performances Comparison                                                                                                                                      | 83                       |

|                                               |                                                                                                                                                                 |                          |

| 4.1                                           | First Track States Table                                                                                                                                        | 96                       |

| 4.1<br>4.2                                    | First Track States Table                                                                                                                                        |                          |

|                                               |                                                                                                                                                                 | 101                      |

| 4.2                                           | Complexity of The Decoding Techniques                                                                                                                           | 101<br>113               |

| 4.2<br>4.3                                    | Complexity of The Decoding Techniques                                                                                                                           | 101<br>113<br>115        |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul> | Complexity of The Decoding Techniques       1         Complexity Comparison of Two Techniques       1         Complexity of One Common Factor Technique       1 | 101<br>113<br>115<br>120 |

# **List of Figures**

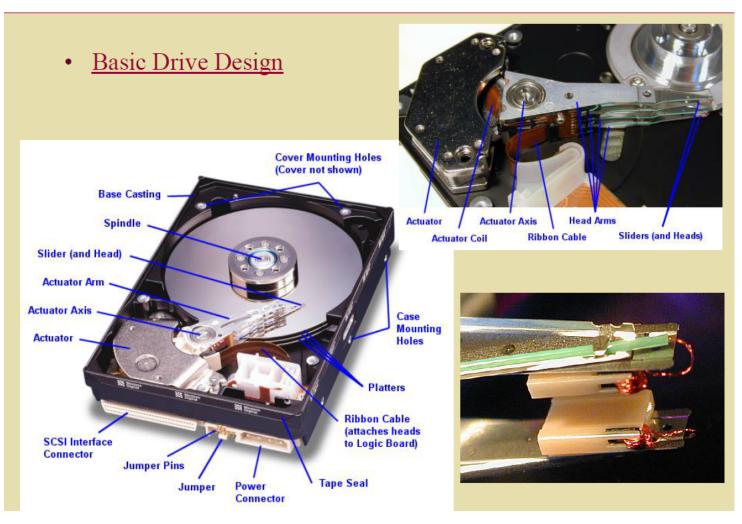

| 1.1 | Hard Disk Drive Parts [2]                                               | 10 |

|-----|-------------------------------------------------------------------------|----|

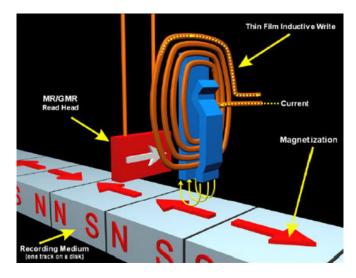

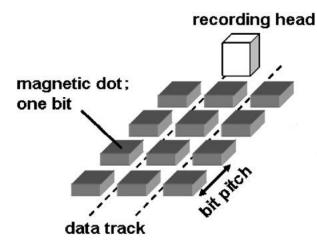

| 1.2 | Longitudinal Magnetic Recording Technology [3]                          | 11 |

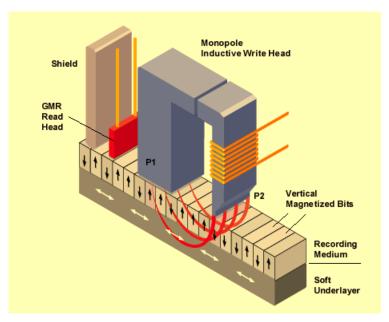

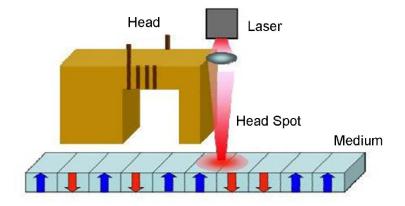

| 1.3 | Perpendicular Magnetic Recording Technology [4]                         | 14 |

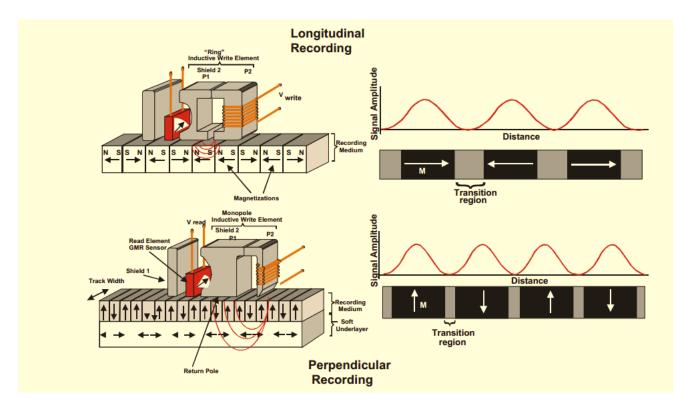

| 1.4 | Main Differences between LMR and PMR [5]                                | 15 |

| 1.5 | Schematic View of the Bit-Patterned Media [6]                           | 17 |

| 1.6 | Schematic View of HAMR Technology [7]                                   | 17 |

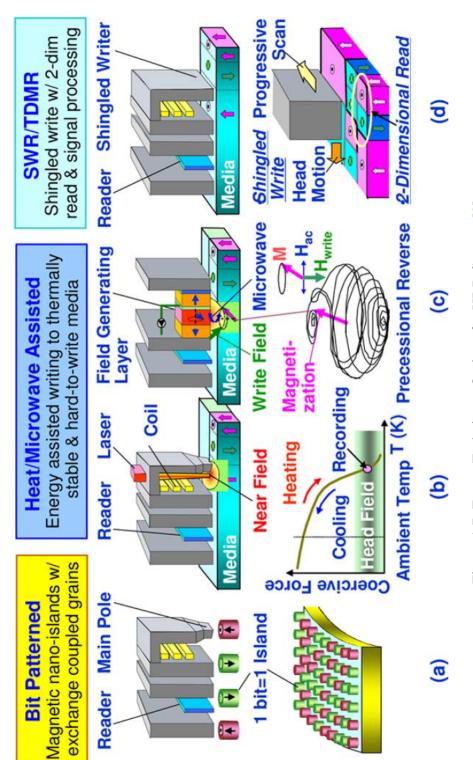

| 1.7 | Future Techniques Options for HDD Storage [8]                           | 18 |

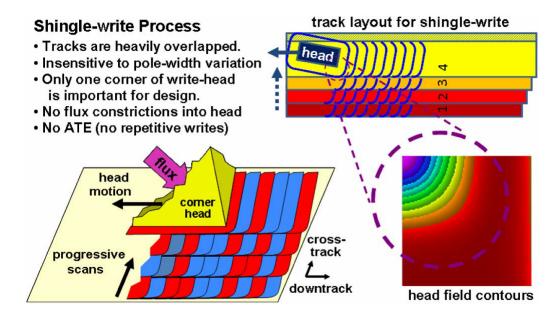

| 1.8 | Shingled Magnetic Recording Technique Process [9]                       | 20 |

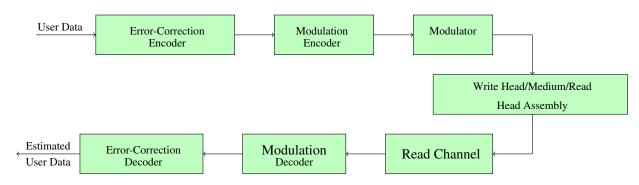

| 2.1 | Data Storage System Block Diagram [10][11]                              | 28 |

| 2.2 | Simulated Longitudinal Recording Channel Model                          |    |

| 2.3 | Sampled Transition Response of Longitudinal Recording at Different Lin- |    |

|     | ear Densities                                                           | 31 |

| 2.4 | Simulated Perpendicular Recording Channel Model                         | 32 |

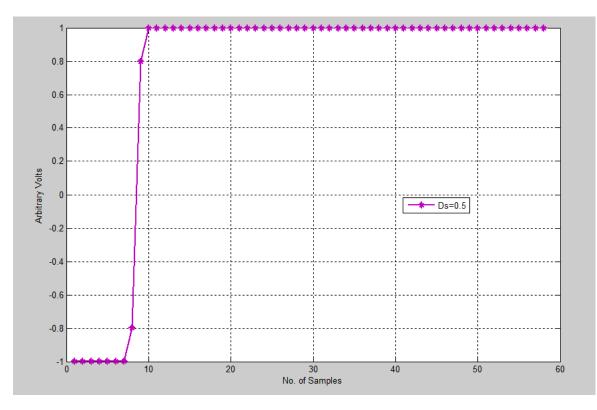

| 2.5 | Sampled Transition Response of Perpendicular Magnetic Recording System  | 34 |

| 2.6 | Sampled Dibit Response of Perpendicular Recording at Different Linear   |    |

|     | Densities                                                               | 35 |

| 2.7 | Block Diagram of Typical PRML Channel [12]                              | 37 |

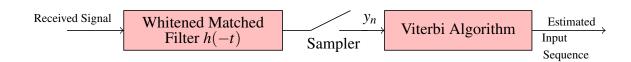

| 2.8 | Optimal Detector Diagram [13]                                           | 43 |

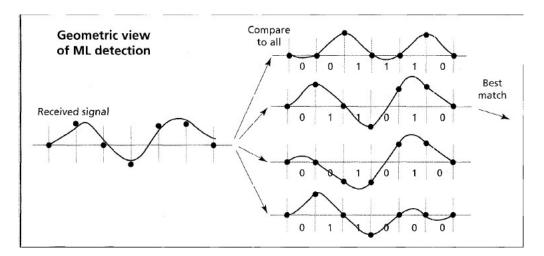

| 2.9 | Geometric view of ML detection [14]                                     | 44 |

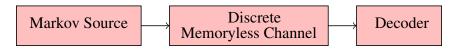

| 2.10 | Schematic Diagram of transmission System [15]                          | 45  |

|------|------------------------------------------------------------------------|-----|

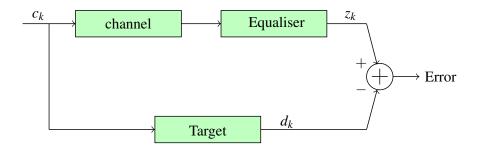

| 3.1  | MMSE Equaliser Design [16]                                             | 50  |

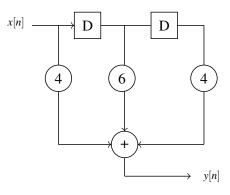

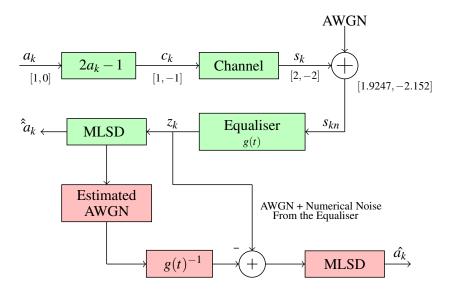

| 3.2  | Block Diagram of the Ideal Channel                                     | 52  |

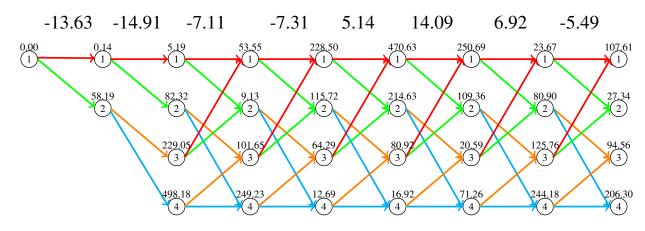

| 3.3  | The GPR trellis diagram                                                | 53  |

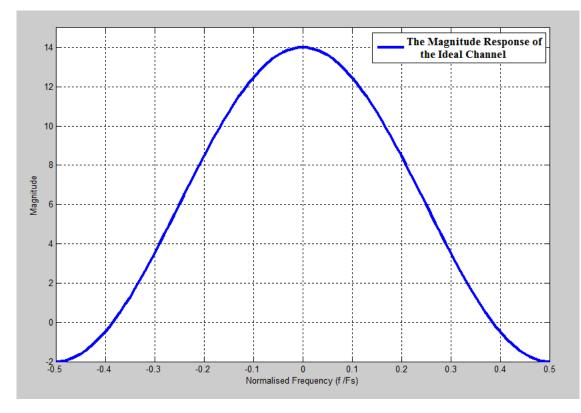

| 3.4  | The Magnitude of the Frequency Response of the Ideal Channel           | 56  |

| 3.5  | A Selection of Normal Distribution pdfs Where Both Mean and Variance   |     |

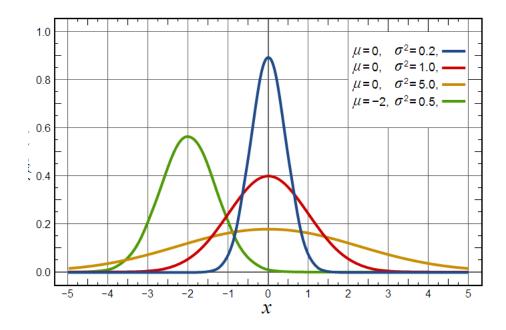

|      | Are Varied [17]                                                        | 59  |

| 3.6  | Memoryless Channel                                                     | 61  |

| 3.7  | Non White Noise Cancellation of AWGN Channel                           | 61  |

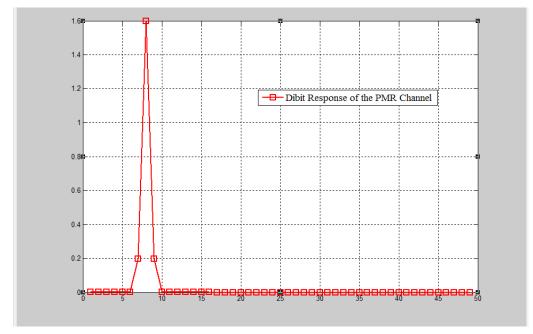

| 3.8  | Sampled Dibit Response of the PMR channel                              | 63  |

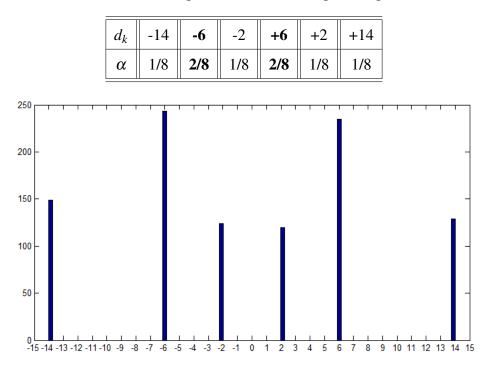

| 3.9  | The pdfs Histogram of The Ideal Output Samples                         | 66  |

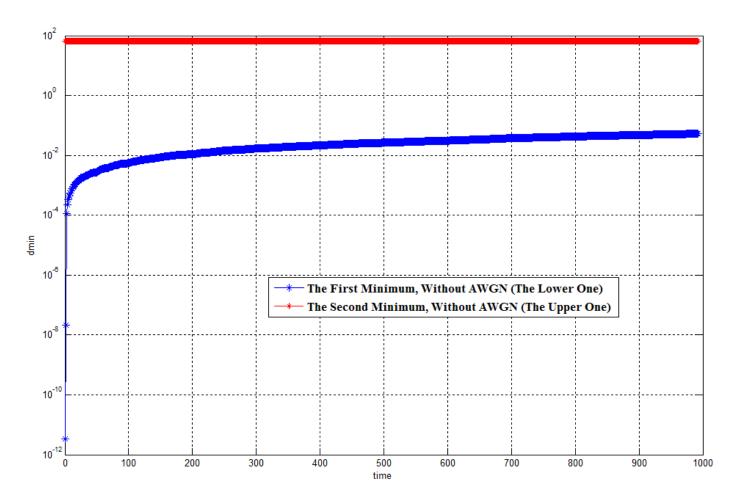

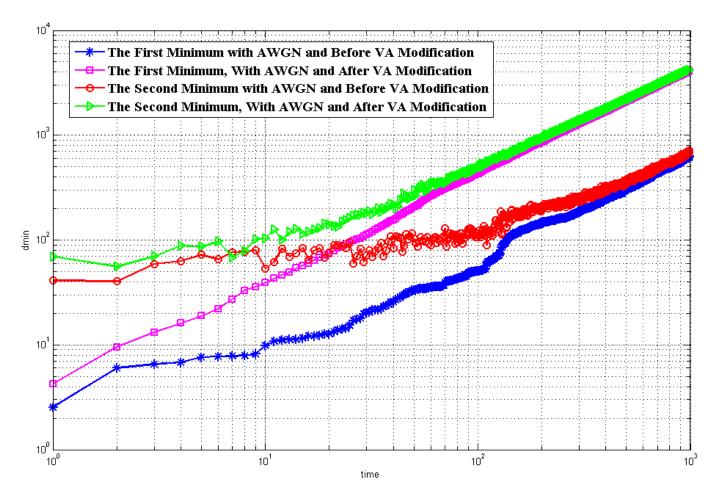

| 3.10 | The First and the Second Minimums for GPR Trellis Without AWGN         | 77  |

| 3.11 | The First and the Second Minimums of VA and Modified VA Trellises      | 78  |

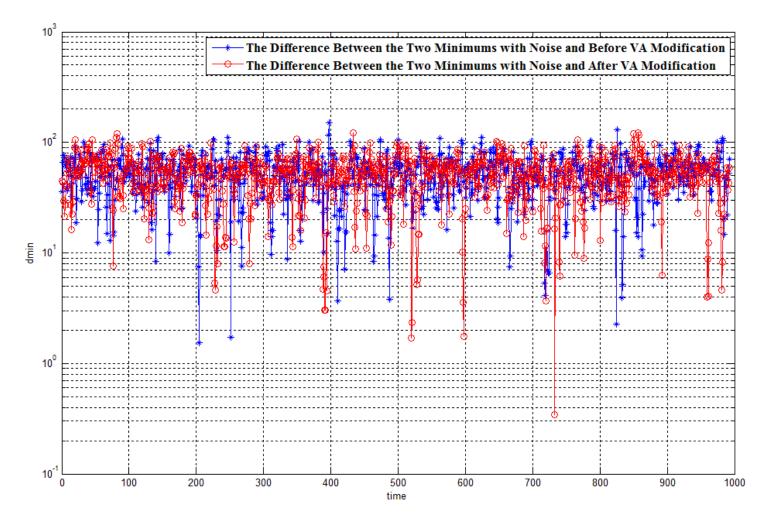

| 3.12 | The Difference Between the First and the Second Minimums of VA and the |     |

|      | Modified VA Trellises                                                  | 79  |

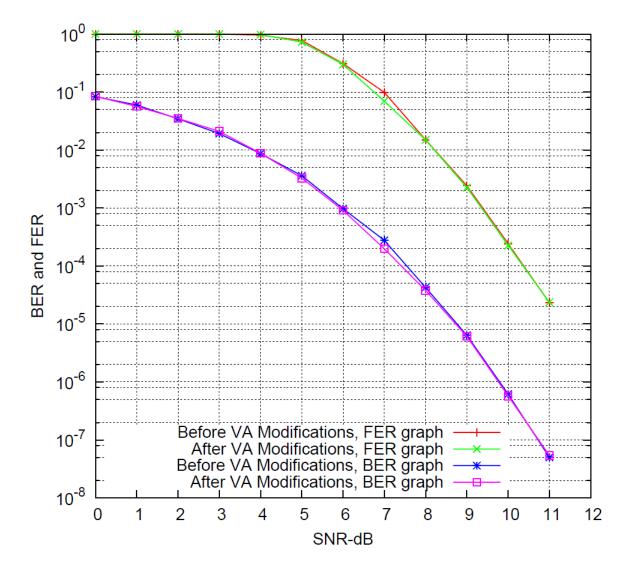

| 3.13 | BER and FER Performances for PRML Before and After VA Modifications    | 81  |

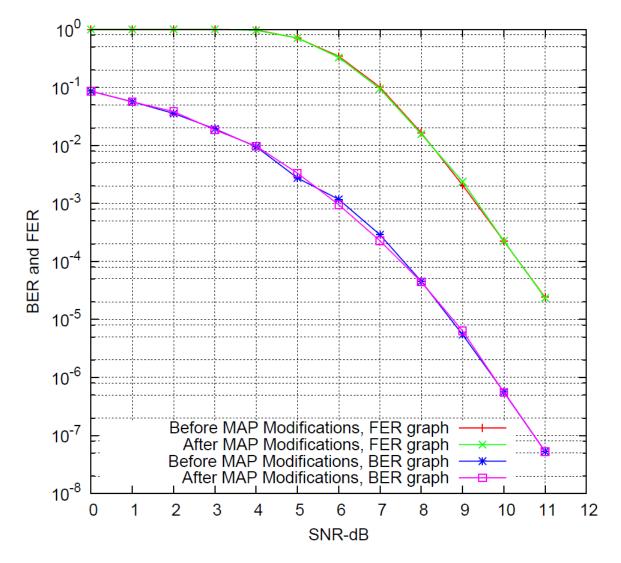

| 3.14 | BER and FER Performances Before and After MAP Modification             | 82  |

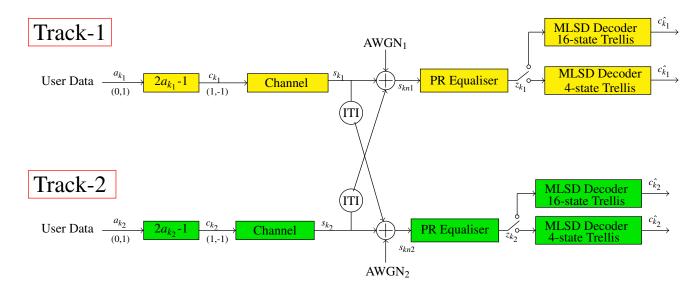

| 4.1  | Shingled Magnetic Recording System Model                               | 91  |

| 4.2  | The 16-state Trellis of the First Track                                | 94  |

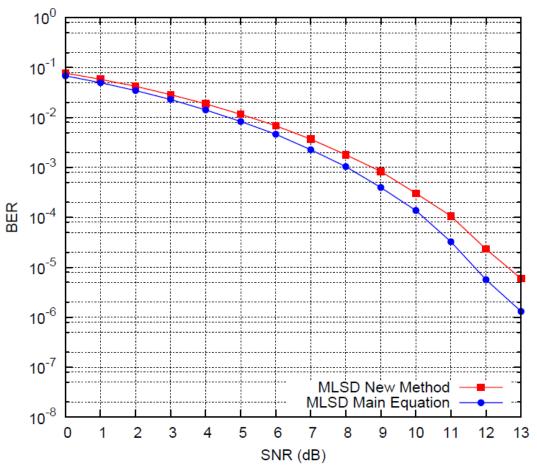

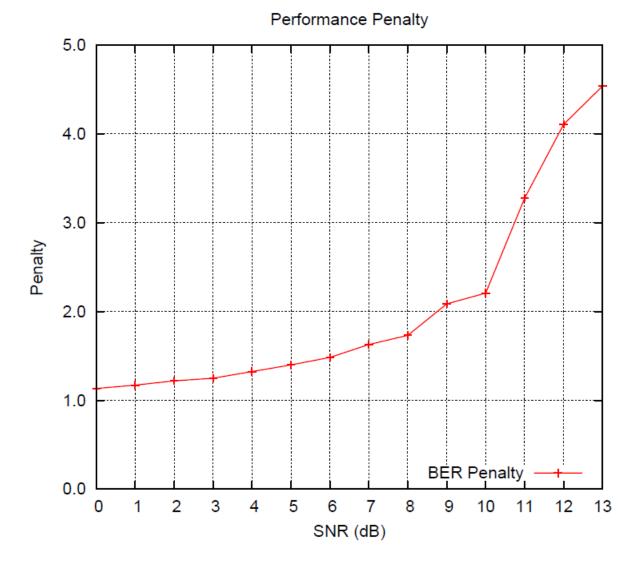

| 4.3  | BER Performance for PRML System With no ITI                            | 102 |

| 4.4  | BER Performance For PRML System Where ITI is Treated as a Noise 1      | 103 |

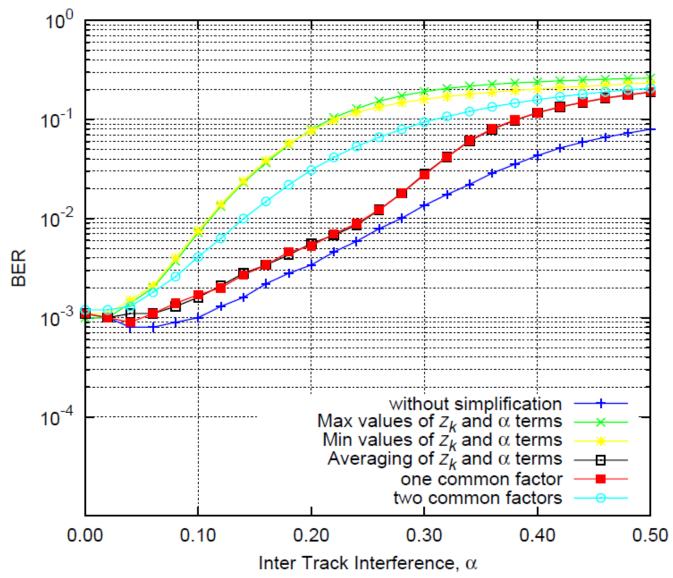

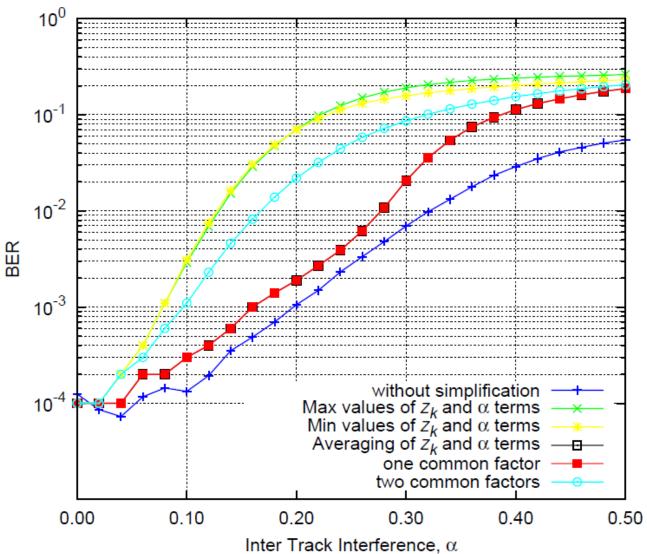

| 4.5  | BER Performance for Shingled System at 6 dB SNR                        | 105 |

| 4.6  | BER Performance for Shingled System at 7.5 dB SNR                      | 106 |

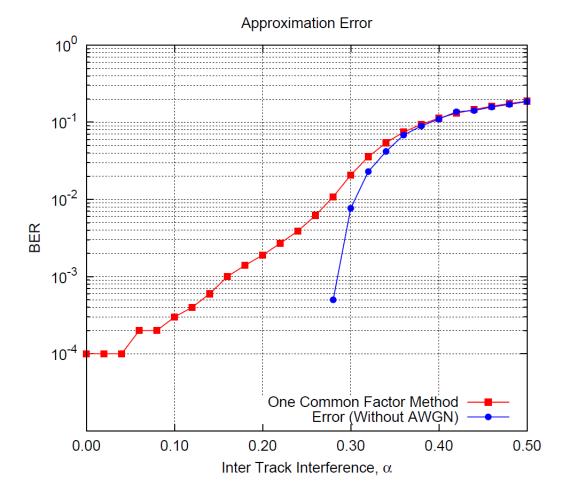

| 4.7  | Performance of One Common Factor Technique With and Without AWGN . 1   | 107 |

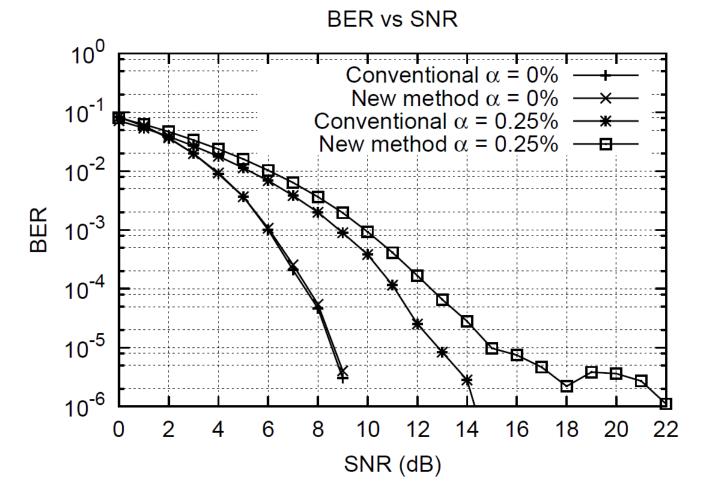

| 4.8  | BER vs SNR for Different Amount of ITI                                 |

|------|------------------------------------------------------------------------|

| 4.9  | BER Performance Comparison                                             |

| 4.10 | The Performance Penalty of One Common Factor Approximation 116         |

| 5.1  | Embedded Multipliers in Cyclone II Devices [18]                        |

| 5.2  | STM32F4DISCOVERY Board [19]                                            |

| 5.3  | FPGA Standard Design Flow [20]                                         |

| 5.4  | Solver Pane of Simulink Software                                       |

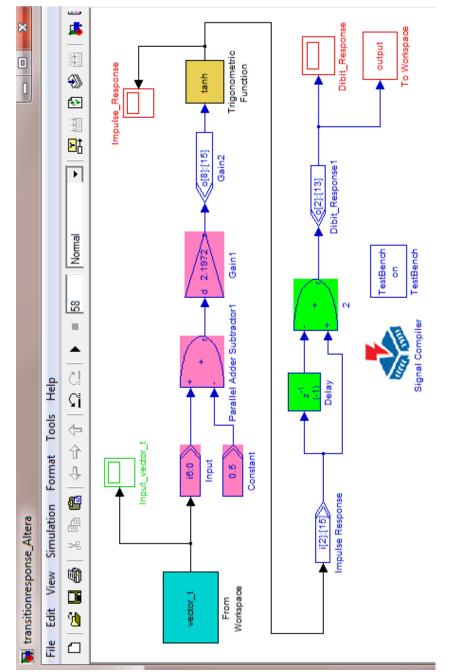

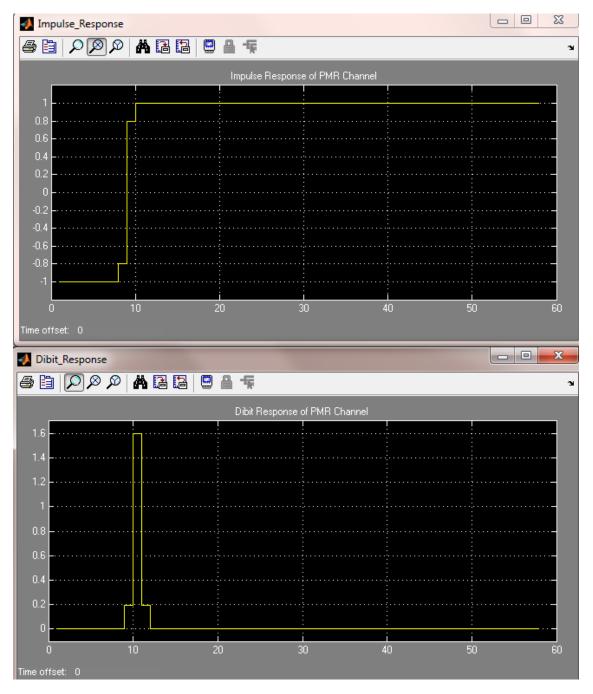

| 6.1  | Simulink Implementation of The Dibit Response of PMR Channel 138       |

| 6.2  | Impulse and Transition Responses of PMR Channel                        |

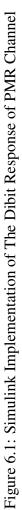

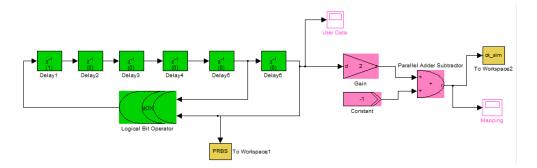

| 6.3  | Simulink Implementation of The Mapping                                 |

| 6.4  | User Data and Mapped Input Sequences                                   |

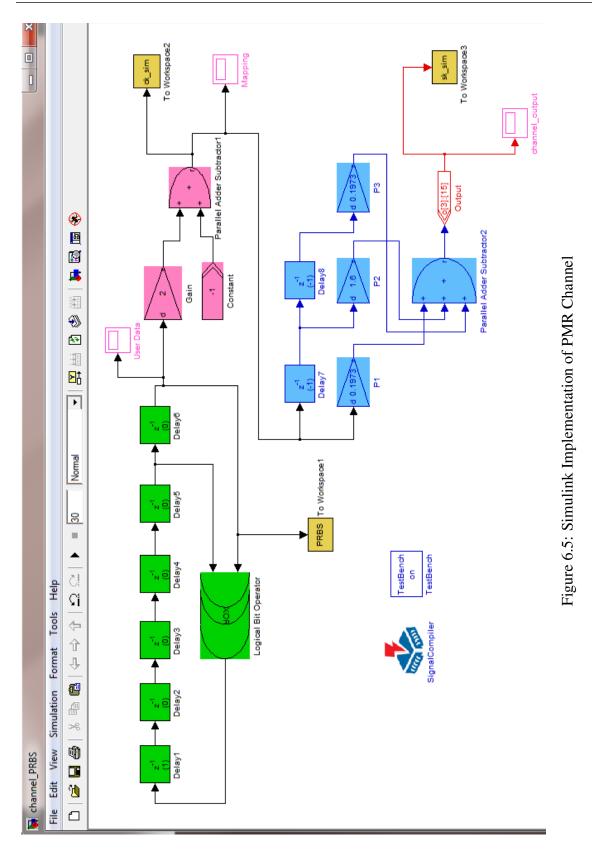

| 6.5  | Simulink Implementation of PMR Channel                                 |

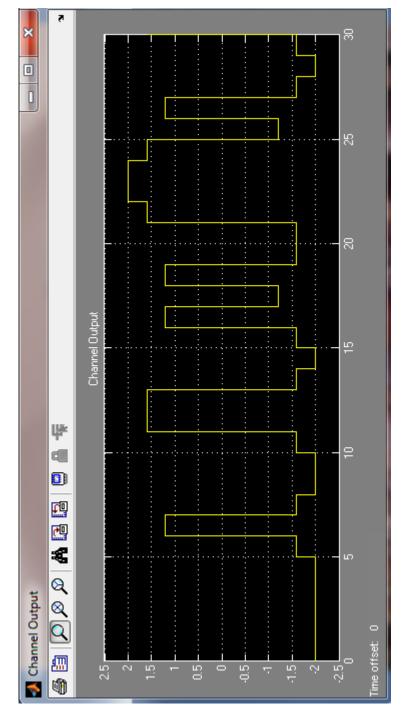

| 6.6  | Simulink Design Output of PMR Channel                                  |

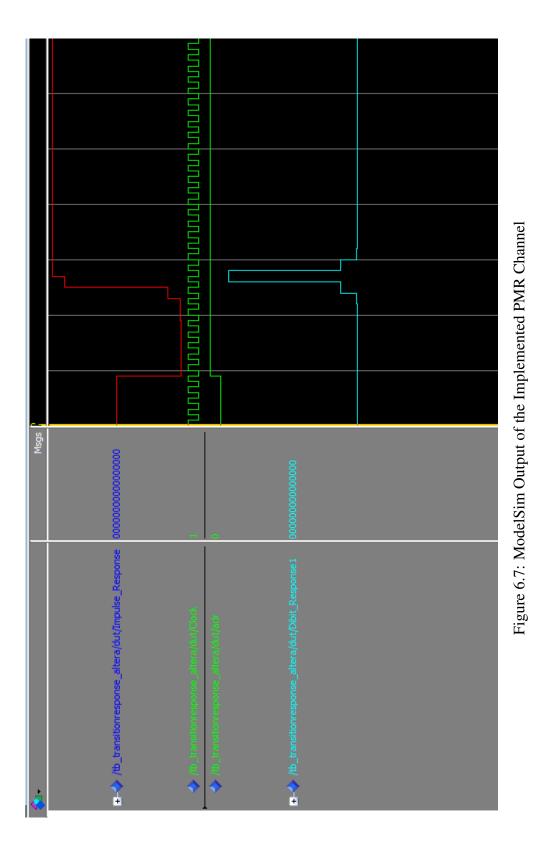

| 6.7  | ModelSim Output of the Implemented PMR Channel                         |

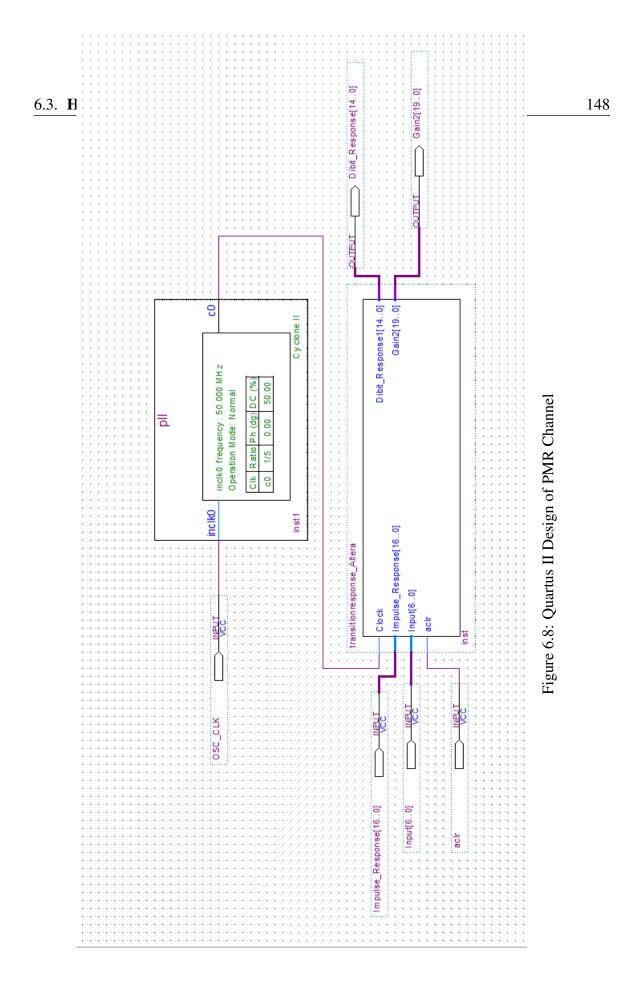

| 6.8  | Quartus II Design of PMR Channel                                       |

| 6.9  | Compilation Report of PMR Channel Quartus II Design                    |

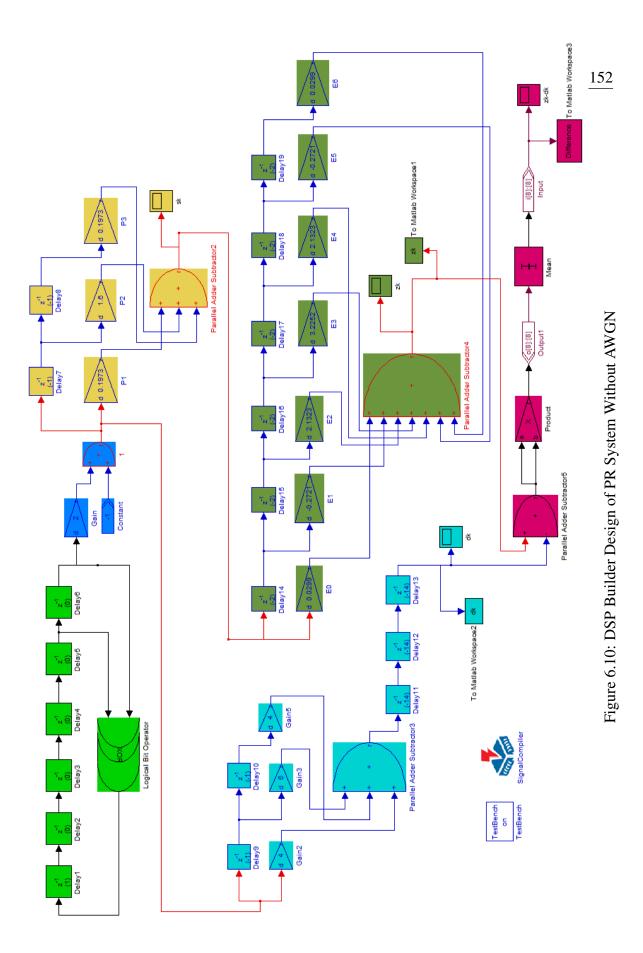

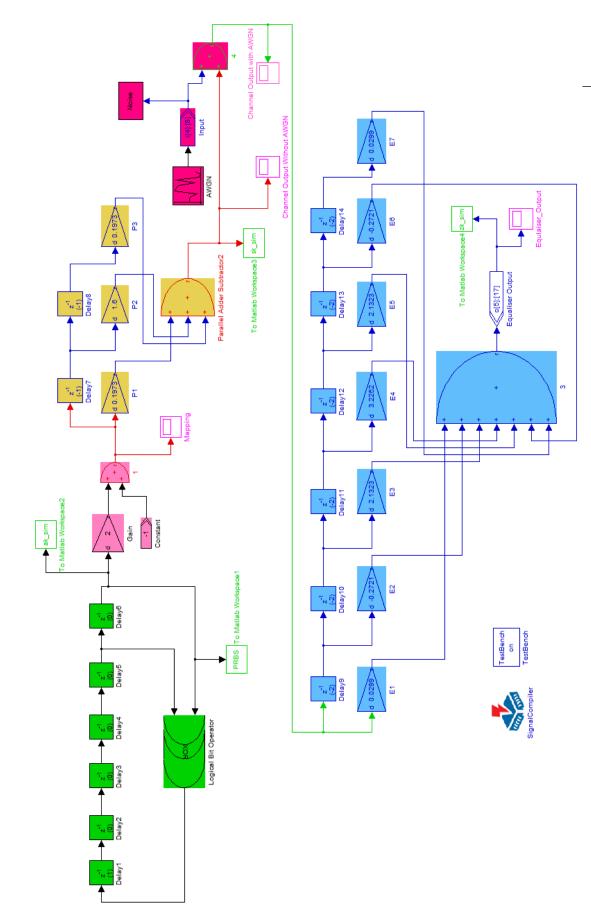

| 6.10 | DSP Builder Design of PR System Without AWGN                           |

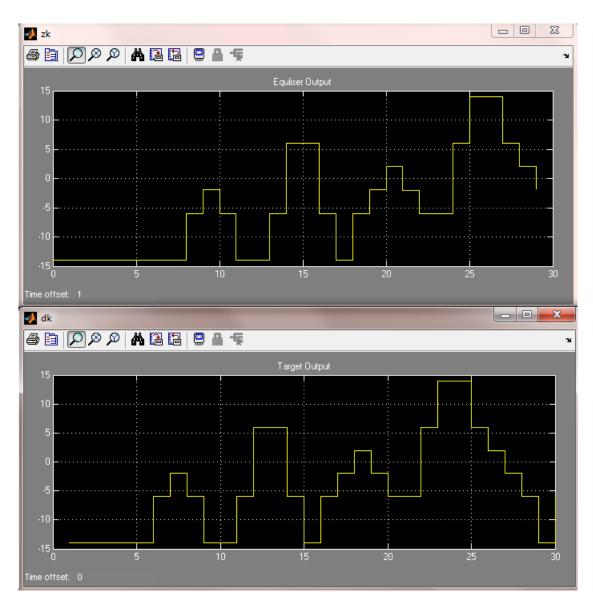

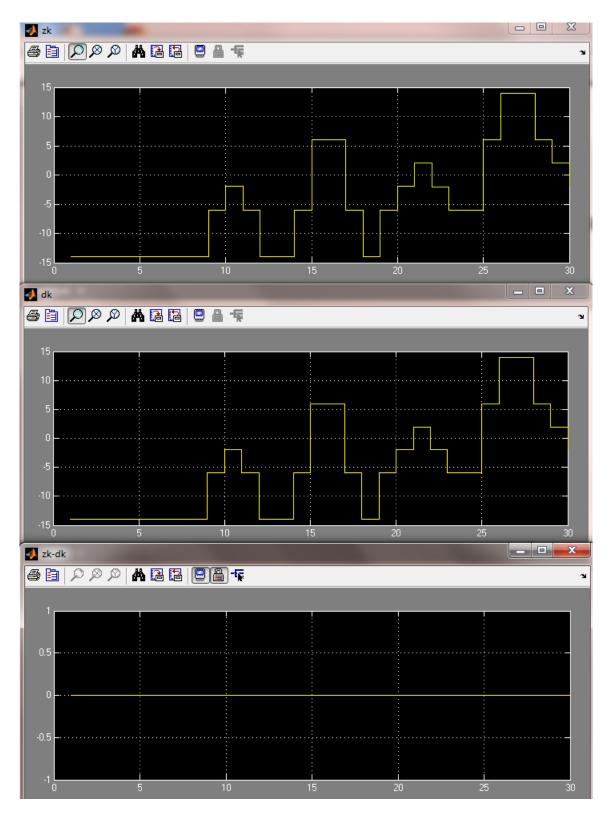

| 6.11 | Equaliser and Target Output Results of Simulink implementation of PR   |

|      | System Without AWGN                                                    |

| 6.12 | The Difference Between Equaliser and Target Sequences of Simulink De-  |

|      | sign of PR System Without AWGN                                         |

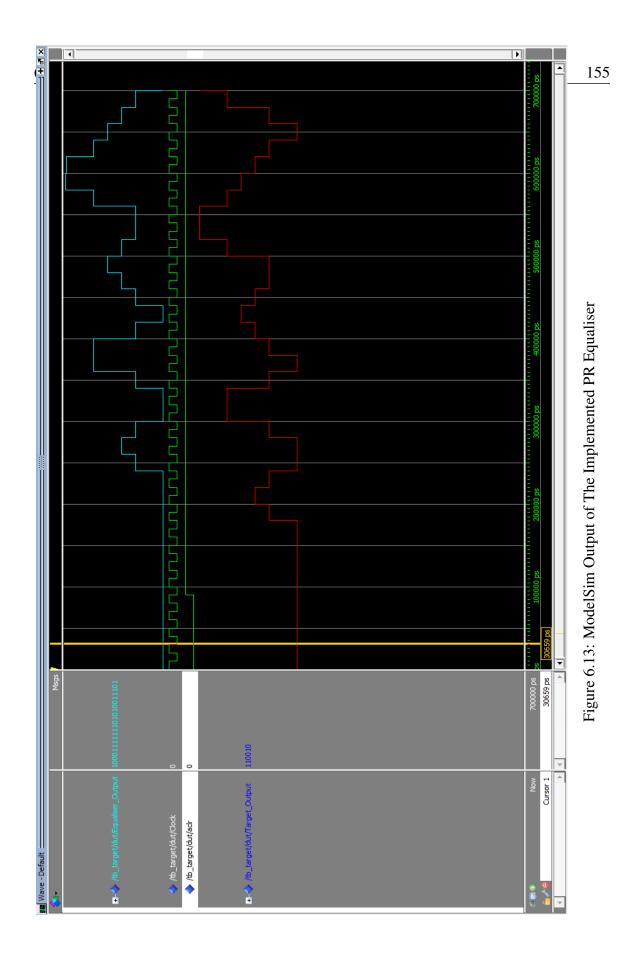

| 6.13 | ModelSim Output of The Implemented PR Equaliser                        |

| 6.14 | Screenshot of Running <i>Testbench</i> Block of PR Simulink Design 156 |

| 6.15 | Complete DSP Builder Design of PR System With AWGN                     |

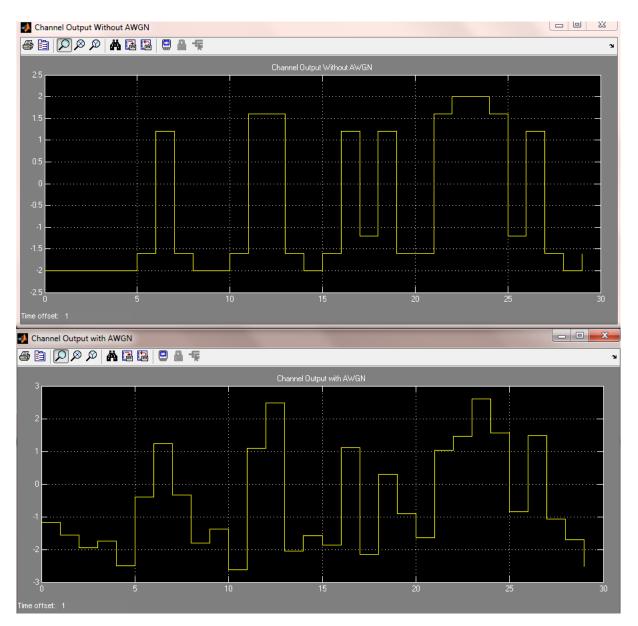

| 6.16 | PMR Channel Output Without and With AWGN                               |

|------|------------------------------------------------------------------------|

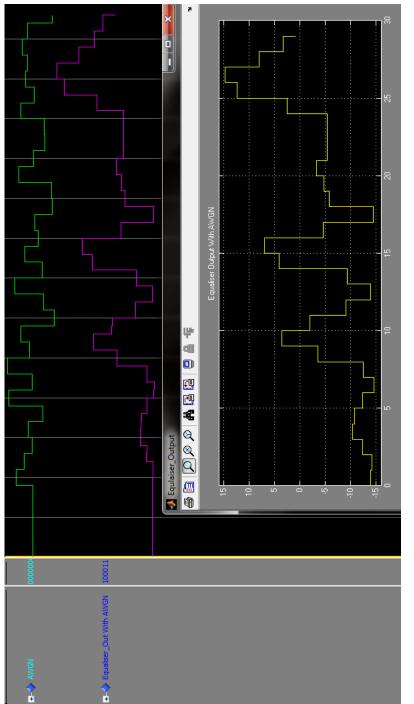

| 6.17 | ModelSim and Simulink Output Sequences of PR System With AWGN 160      |

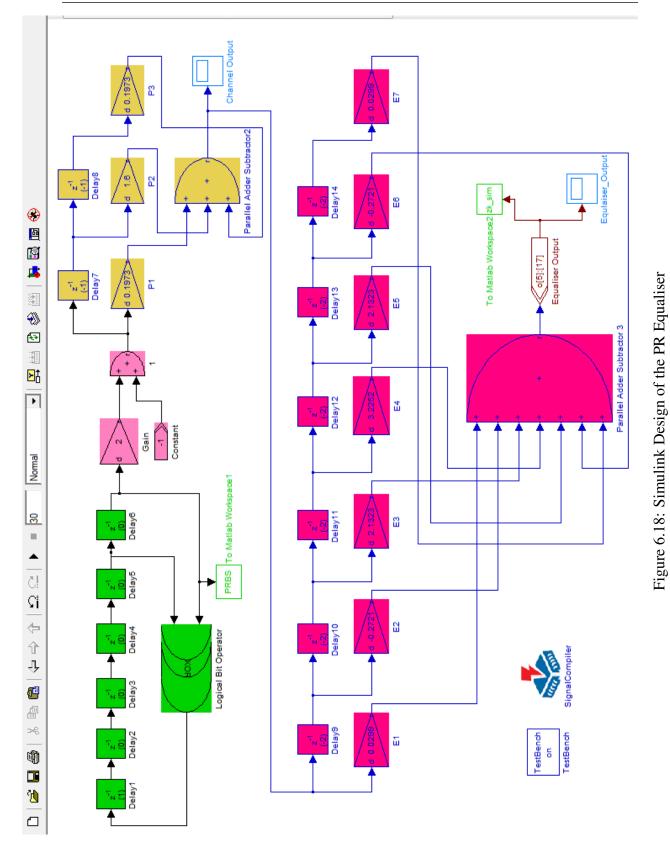

| 6.18 | Simulink Design of the PR Equaliser                                    |

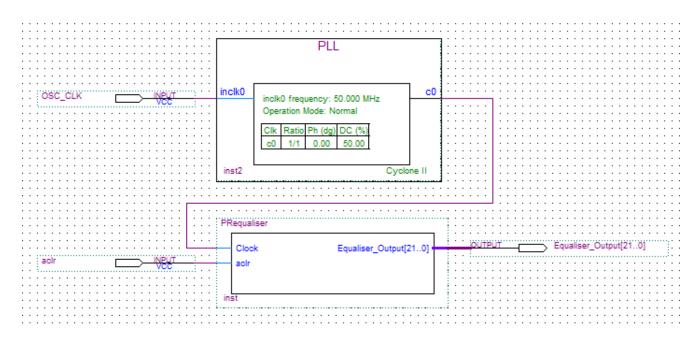

| 6.19 | Quartus II Design of the PR Equaliser                                  |

| 6.20 | FPGA Chip Pin Assignments of PR Equaliser Design                       |

| 6.21 | Compilation Report of PR Equaliser Quartus II Design                   |

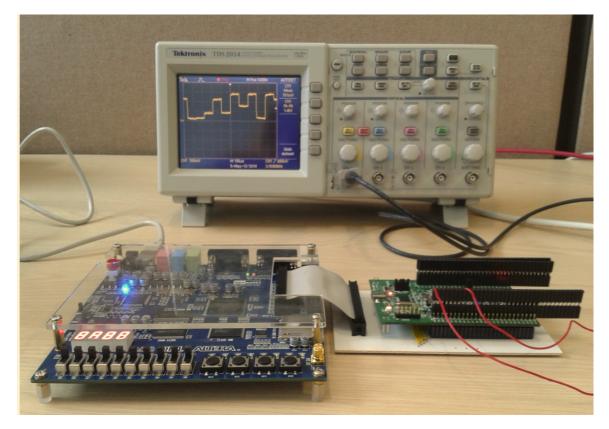

| 6.22 | Hardware Verifying of PR Equaliser Design Model                        |

| 6.23 | The Implemented GPR trellis in Simulink                                |

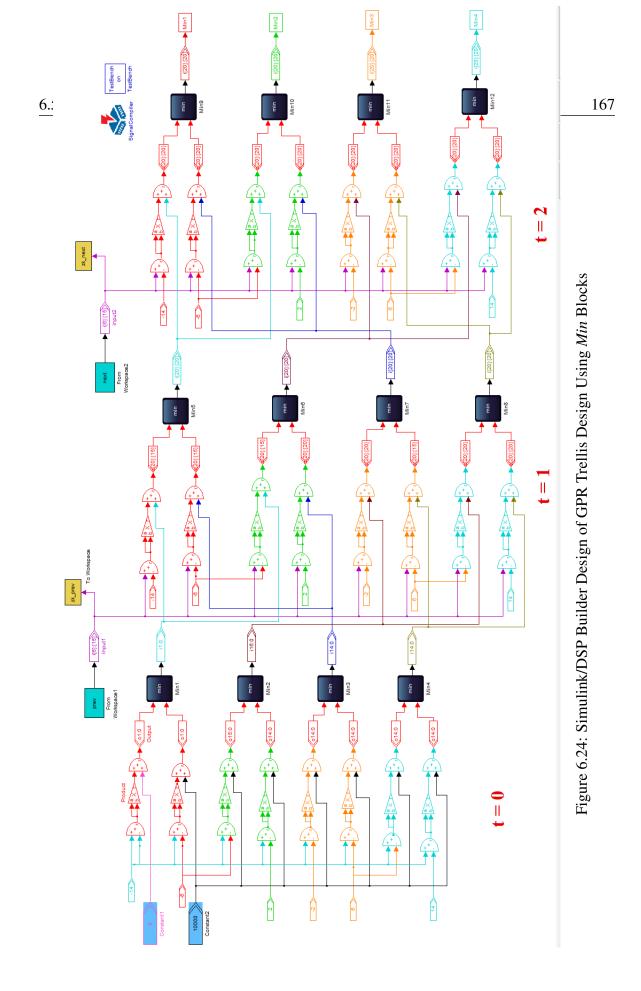

| 6.24 | Simulink/DSP Builder Design of GPR Trellis Design Using Min Blocks 167 |

| 6.25 | Compilation Report of VA Simulink Design Using Min Blocks 168          |

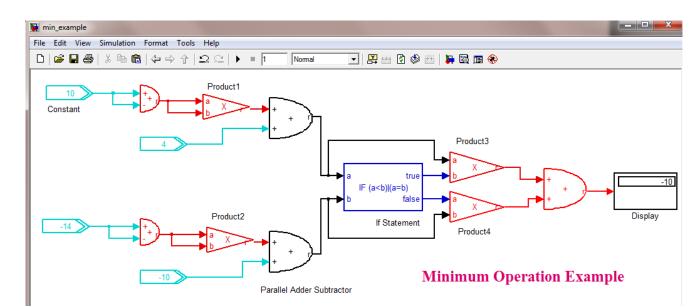

| 6.26 | Example of Implementation One Minimum Operation of 4-state Trellis 170 |

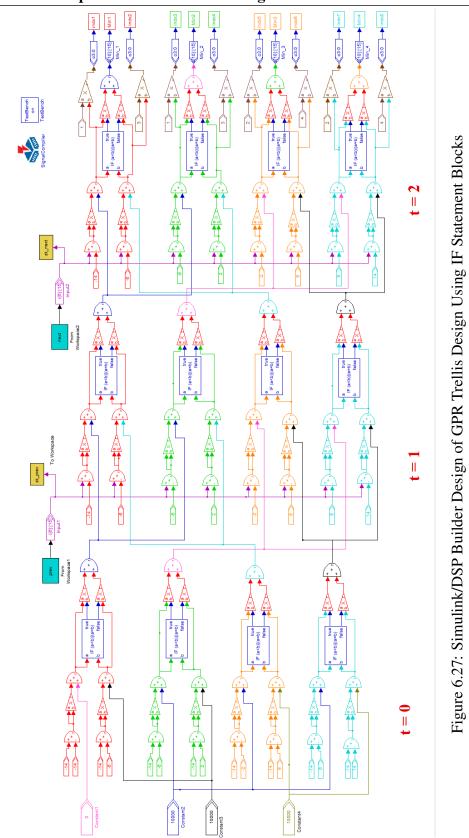

| 6.27 | Simulink/DSP Builder Design of GPR Trellis Design Using IF Statement   |

|      | Blocks                                                                 |

| 6.28 | Compilation Report of VA Simulink Design Using IF Statement Blocks 173 |

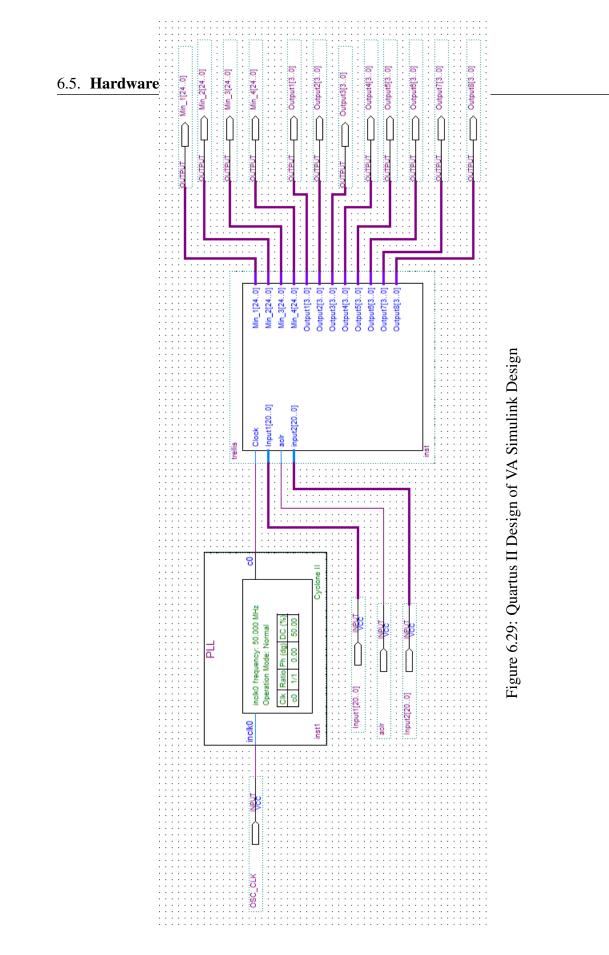

| 6.29 | Quartus II Design of VA Simulink Design                                |

| 6.30 | Compilation Report of VA Quartus II Design                             |

# **Abbreviations**

- 2-D Two-Dimensional

- ADC Analog-to-Digital Converter

- APP A Posteriori Probabilities

- AWGN Additive White Gaussian Noise

- BER Bit Error Rate

- BPM Bit-Patterned Media

- CTF Continuous Time Filter

- DAC Digital-to-Analog Converter

- DSP Digital Signal Processing

- FIR Finite Impulse Response

- FPGA Field-Programmable Gate Array

- GMR Giant Magneto-Resistance

- GPR Generalized Partial Response

- GPR3 Class-III Generalized Partial Response

- GUI Graphical User Interface

- HAMR Heat-Assisted Magnetic Recording

- HDD Hard Disk Drive

- HDL Hardware Description Language

- ISI Inter Symbol Interference

- ITI Inter Track Interference

- LMR Longitudinal Magnetic Recording

- MAMR Microwave Assisted Magnetic Recording

- MAP Maximum A Posteriori

- ML Maximum Likelihood

- MLSD Maximum-Likelihood Sequence Detection

- MMSE Minimum Mean-Square Error

- MR Magneto Resistive

- OTI Off-Track Interference

- pdf probability density function

- PMR Perpendicular Magnetic Recording

- PR Partial Response

- PR4 Class IV Partial Response

- PRBS Pseudo Random Binary Sequence

- PRML Partial Response Maximum Likelihood

- RLL Run-Length-Limited

- RTL Register-Transfer Level

- SMR Shingled Magnetic Recording

- SNR Signal to Noise Ratio

- SUL Soft Magnetic Underlayer

- TDMR Two-Dimensional Magnetic Recording

- VA Viterbi Algorithm

- VGA Variable-Gain Amplifier

- VHDL Very high speed integrated circuits (VHSIC) Hardware Description Language

# **Chapter 1**

## Introduction

The digital lifestyle which includes accessing the internet, using cash machines, watching Hollywood movies and trading stocks online demand tremendous amounts of digital information. Most information is stored in four types of physical media that are: paper (books and newspapers), film (photographs and cinema), optical (DVDs) and magnetic (PC disk drives and camcorder tape) [21]. However, magnetic storage is the largest medium used for storing information [21].

According to the study of University of California-Berkeley in 2003, the world produces between 1 and 2 exabytes (exabyte is a billion gigabytes or  $10^{18}$ ) of unique information per year (about 250 megabytes per person) [21]. Then, another study was forecasted explosive growth of the digital universe from  $281 \times 10^{18}$  (281 exabytes) in 2007 (about 45 GB per person) to  $1.8 \times 10^{21}$  (1.8 Zetta) Bytes in 2011 [8]. Thus, it is necessary to ensure the rapid increase in the capacity of HDD.

In 1999, The First 100 Years book was published on the 100<sup>th</sup> anniversary of the data storage technologies. Data storage area could be considered as a very mature area whose trend in magnetic recording has focused on smaller, faster, cheaper and denser devices.

A brief history of Hard Disk Drive (HDD) is outlined in this chapter followed by reviewing the magnetic recording technologies. The main purpose of this work and the contributions that the author achieved are outlined in aim and objectives and contribution to knowledge sections.

#### **1.1 History of Hard Disk Drive**

This section highlights some of the historical events that happened in the field of hard disk storage which had resulted to increase the storage capacity such as:

- 1888- the first magnetic recording head was invented by Oberlin Smith. Then in 1898, Valdemar Poulsen built the first functioning recorder using Oberlin head design [10].

- 1956- the first commercial HDD was invented by IBM with a storage capacity of five million characters [22].

- 1961- Model 1301 disk drive was shipped by IBM with a capacity of 56 MB [10].

- 1971- Magneto Resistive (MR) head was discovered which accelerated HDD development 20 years later [23]. However, the MR effect was first found in 1857 [2] and the 2007 Nobel prize in physics was awarded to scientists who discovered the MR effect [24]. The first use of the MR head in commercial disk drive was developed by IBM in 1992 [10].

The design of MR head is based on the concept of the ability of metals to change their resistivity in the presence of a magnetic field [2] [25].

During readback process, the recorded magnetic patterns that are represented by the alternating magnetic pols N and S create fringing magnetic fields. The read head senses these fields which causes a change in the resistance of the stripe on the MR head. Consequently, an output voltage is produced that varies according to that magnetic patterns [24].

• 1972- The structure of ML estimator was introduced [26].

- 1974- BCJR algorithm, named after the authors (Bahl, Cocke, Jelinek and Raviv) of [15], was developed to minimize the probability of symbol (or bit) error on trellis based constraints.

- 1976- A magnetic head for perpendicular recording was proposed by Iwasaki, *et al* [27]. It consists of two poles, the main pole for recording and the auxiliary pole. This head produces a field whose perpendicular component has an intensive and sharp distribution.

- 1979- VA was possible to apply in magnetic recording systems for detection purposes [10].

- 1979- IBM 3370 introduced thin film heads technology however working on thinfilm head structures was started in the late-1960s [28].

- 1990- First HDD with Partial Response Maximum Likelihood (PRML) algorithm was introduced by IBM [10].

- 1992- Marcellin and Weber introduced two-dimensional modulation code which increased the data storage density by working on multiple tracks in parallel [29]. However, Swanson and Wolf introduced a new class of two-dimensional Run-Length-Limited (RLL) recording codes that added an additional constraint across each track [30].

- 2001- Different types of target for PRML channel were investigated in [31]. The paper confirmed that the Class-III-based Generalized Partial Response (GPR3) target had a better performance.

- 2001- Wood, *et al.* in [32] confirmed that the media characteristics of perpendicular recording have a significant effect on the areal densities.

- 2002- Seagate applied Heat-Assisted Magnetic Recording (HAMR) technology into HDD by cramming one Terabit into a square inch [33].

- 2005- Toshiba shipped the first HDD using PMR technology. This new technology was applied into two high capacity drives: 1.8" 40/80 GB [34].

- 2006- A new optical drive element was developed by Fujitsu using HAMR [35].

- 2007- HGST announced industry's first Terabyte hard drive using PMR technology [36].

- 2008- Seagate unveiled the industry's first 1.5TB desktop and 0.5TB notebook hard drives [37]

- 2010- Western Digital announced shipping 3TB internal hard disk drive [38].

- 2011- Seagate shipped the first 4TB external HDD [39].

- 2012 Western Digital announced the first 2.5-inch, 5*mm* thick drive, and the first 2.5-inch, 7*mm* thick drive with two platters [40].

- 2012 TDK demonstrated 2TB on a single 3.5-inch platter using HAMR technology [41].

### **1.2** Communication Channel for Magnetic Storage

Communications mean transmission of information from a source to a destination through a channel. Depending on the physical medium that uses to transmit these information, different types of channels are there such as:

1. **Wireline channels**: like wire lines for voice signal transmission of telephone network and twisted-pair wire lines and coaxial cable for electromagnetic channels.

- 2. **Fiber optic channels**: the information is carried on a modulated light beam. The bandwidth of these channels is larger than coaxial cable channels which offers a wide variety of telecommunication services such as voice, data, facsimile and video.

- 3. **Wireless electromagnetic channels**: transmit the information using electromagnetic waves through the atmosphere (free space) by radiating them via antenna.

- 4. **Underwater acoustic channels**: data transmission is performed by sensors placed under water which transmit the data to the surface of the ocean.

- 5. **Storage channels**: include magnetic tape (digital audio tape and video tape), magnetic disks, optical disks and compact disks which can be considered as communication channels where the data are written on a disk and then read out at a later time.

The difference between data storage channel and communication channel is the domain in which the communication occurs. For the data storage channel, the communication is represented in time domain where, the information is transported from one time to another. However, different domains are used for the communication channels as mentioned above. Furthermore, there is a big difference between the two channels in terms of Bit Error Rate (BER) . In communication systems, the BER would be  $10^{-5}$  or  $10^{-6}$ . In contrast,  $10^{-12}$ error rate or better is the BER requirement for storage systems [42].

### **1.3 Data Storage Devices**

Permanent storage device stores data (information) permanently unless it is physically changed or deleted by the user. Therefore, this information will not be lost when the power is switched off. On contrast, in read access memory (RAM) the information will be lost when the power is turned off. The most common permanent storage devices are: magnetic

disk, optical disk, magnetic tape, flash memory, floppy disk, solid-state drive, hybrid drive and external drives.

These devices could be classified according to their capacity, portability and the access method. Access method means the way by which data would be accessed which is either directly or sequentially. Magnetic tape is an example of sequential access media. In order to get a specific data, the user should roll through the tape until the desired data is located. However, for the direct access devices, the user can get a particular data directly without passing through a sequence. Best example of direct access devices is the HDD. The following section depicts the parts of the HDD.

#### **1.4 Hard Disk Drive Components**

HDD consists of many parts as depicted in Figure 1.1. The main part is the platter [43]. Platters are rotating disks made of an aluminium or glass and ceramic substrate which are held by a spindle spinning at an extremely high speed. Platters, unlike the floppy disks, cannot be flipped or bent that is why they have been called hard disks. Normally, HDD have 1 to 10 identical platters each one has one write/read head. The magnetic layer on the platter is divided into a very small room, each room stores one bit of data. The two sides of each platter are magnetized to store the information and this would increase the storage density. Also, the key component of the HDD is the head that performs writing and reading functions. Head writes the data by converting the electrical current into a magnetic field which magnetizes the storage medium into two opposite directions. To read the recorded data, the head senses the magnetic flux from the media. Head flies over the disk surface with a distance called flying height which is about  $20\mu$ in [10]. The first head used was Poulsen-type head [23], where longitudinal recording was done by this head. Then using ring-type head improved the recording performance [23]. Lee, *et al.* [44] proposed a

Figure 1.1: Hard Disk Drive Parts [2]

modified ring-head. The proposed channel model was for a single-layered perpendicular magnetic recording with a modified ring-head. The ring-head has been trimmed at the top pole edge to get a new head with improvements of the perpendicular head field and its gradient.

Recording data on a hard disk drive is accomplished by writing it on the recording medium. The medium would be magnetized into two opposite directions by passing a current into the write head. The two opposite directions representing either 0 or 1. The recording medium should be thin and highly coercive to allow recording of large amount

Figure 1.2: Longitudinal Magnetic Recording Technology [3]

of data onto the disk surface. Firstly, the coated r-Fe<sub>2</sub>O<sub>3</sub> film of thickness less than 1 $\mu$ m was used. Then, composite anisotropy medium composed by double layers of Fe-Ni and Co-Cr thin films were prepared by Iwasaki, *et al.* [27] which had a significant effect in increasing the storage capacity.

### 1.5 Longitudinal Recording Technology

Depending on the way the recording medium is saturated, there are three types of magnetic recording which are longitudinal, perpendicular and transverse. The recording types are classified according to the direction of magnetization relative to the direction of the medium motion [22]. Longitudinal thin film recording has been the standard technique in the HDD industry for more than 50 years [45]. In Longitudinal Magnetic Recording (LMR) technique, the data bits are aligned horizontally in relation to the plane of the disk as shown in Figure 1.2. This method has reached its physical limit and the maximum storage density could be offered is 100 Gbit/in<sup>2</sup> by using *Ku* materials (uniaxial magnetocrystalline anisotropy) [46][47]. Therefore, the necessity of a new method was arisen to meet data growth requirements. PMR, which was known before longitudinal recording [48], was the alternative attention for HDD industry.

In general, increasing the storage capacity needs several requirements such as:

- Medium requirements which include thickness with high coercivity. Coercivity means the capability of a ferromagnetic material to be demagnetized. Demagnetization in the medium decreases the remanent magnetization and establishes circular magnetization mode which in turn reduces the reproduced signals [49]. Consequently, reducing the thickness of the recording medium could prevent the establishing of the circular magnetization.

- 2. Low thermal stability: the magnetic medium consists of grains. Increasing the storage capacity requires shrinking the grains further which leads to the thermal stability problem. That means the grains would be much taller than they are wide. Therefore, a specific volume should be available for those grains to be thermally stable [9]. Also, making the grains so small would affect the energy of the signal itself. In other words, signal energy becomes very small compared to the ambient thermal stability which in turn requires powerful signal processing tools to retrieve the recorded bits [50].

- 3. Head requirements like strong writing field of the inductive head.

- 4. Good Signal to Noise Ratio (SNR) which satisfy BER requirements. However, error rate of  $10^{-12}$  or less is the need for storage systems [51].

- 5. Advanced signal processing tools to reliably retrieve the readback signal. Increasing the storage density would cause many sources of noise and distortion such as transition jitter noise, electronics noise in the head and preamp circuits, recording medium

noise [10], ISI and ITI. Consequently, appropriate mitigation techniques are required to retrieve back the recorded signal.

Iwasaki, *et al.* [49] analysed the demagnetization mechanism of the longitudinal recording in high density storage. The conclusion that came from this analysis was that the longitudinal recording is no longer the best method in terms of high storage density. An experiment of combining perpendicular anisotropy films with magnetic heads was performed by Iwasaki, *et al.* which confirmed that the perpendicular recording had a magnetization mode which increased the remanent magnetic moment of signals.

To counter the above problems, PMR technology was introduced by Iwasaki. The following section will explain this technology (PMR) and then shows the limitations and alternatives for it.

### 1.6 Perpendicular Recording Technology

It is mentioned that the first HDD using PMR technology was shipped in 2005 which boosted the capacity to 80 GB [34]. The longitudinal recording method was replaced by perpendicular recording because it reached its physical limits due to the superparamagnetic effects [48][31] [52]. The superparamagnetic effect is a trade-off between three parameters: the thermal stability of the media, the write ability of the media with a narrow track head and the media SNR [8]. However, perpendicular and longitudinal recording methods have complementary relationship even in the aspect of engineering. The perpendicular recording magnetization mode is suitable for recording of the digital signal while for the analog signal, the longitudinal recording magnetization mode is more suited [27]. In this technique, the data bits are aligned perpendicularly in relation to the plane of the disk as shown in Figure 1.3 which allows picking up more data on a disk surface compared with the longitudinal magnetic recording [53].

Figure 1.3: Perpendicular Magnetic Recording Technology [4]

### 1.6.1 PMR Advantages Over LMR

PMR have several advantages over LMR such as:

- Perpendicular recording system uses single-pole type write head which gives twice the field that a ring head produces [32][50]. Higher write field would increase the write efficiency [10] and subsequently increase the storage density.

- In PMR, the bits are thermally more stable than in LMR as the adjacent bits are placed side by side rather than end-to-end which allow attraction the bits instead of rejection.

- Adding a Soft Magnetic Underlayer (SUL) beneath the recording layer (PMR includes two groups with and without SUL [10]) offers a larger effective write field which has a significant effect on increasing the data storage [53].

- Both technologies use the same read head which is Giant Magneto-Resistance (GMR)

Figure 1.4: Main Differences between LMR and PMR [5]

playback sensor.

The main differences between the two technologies are depicted in Figure 1.4. All these benefits make PMR more interested than LMR and one of the assuring magnetic recording systems for the HDD.

Using PMR, two ways could help to increase the storage capacity of HDD which are either increasing the areal density of the platter or increasing the number of platters.

Areal density is defined as the number of bits per inch per track times tracks per inch [45] which is given in bits/mm<sup>2</sup>, Mbit/in<sup>2</sup>, Gbit/in<sup>2</sup> and Tbit/in<sup>2</sup> [54].

However, PMR technology has some limitations against increasing the storage capacity such as the instability of the medium in case make magnetised areas are very small. Also, because of the other technologies like: Bit-Patterned Media (BPM), HAMR and Microwave Assisted Magnetic Recording (MAMR) require the medium to be redesigned which in turn require high expenses. Thus, the direction now is towards adding platers to increase the storage capacity rather than cramming more bits on the same platter [55].

Wood [50] suggested that achieving 1 Tbit/in<sup>2</sup> is feasible for PMR method. The fundamental obstacle to go beyond this achievement for this technology is the superparamagnetic effect [50].

Recently, some HDD industry projects have started which aim at pushing the storage density beyond the superparamagnetic limit for example: in 2010, the Storage Research Consortium project aimed at 2 Tbit/in<sup>2</sup>, in 2013 the New Energy and Industrial Technology Development Organization target at 5 Tbit/in<sup>2</sup> and 10 Tbit/in<sup>2</sup> by 2015 for Information Storage Industry Consortium [8].

### 1.7 Future Technology Options

Some approaches have been considered as an alternative to the conventional technique (PMR) such as BPM, HAMR/MAMR and SMR . BPM looks a promising technique to continue beyond the 1 Tbit/in<sup>2</sup> and eliminates the limitations of PMR that were mentioned in section 1.6. In this technology, the magnetic layer (medium) must be radically redesigned i.e. continuous thin film should be replaced with a discrete magnetic material [45]. However, this approach faces some challenges which make it difficult to implement. The first challenge is manufacturing the medium and engineering it into islands [56] as shown in Figure 1.5 [45]. BPM suggests storing one bit in one magnetic island [8] unlike PMR where each bit must cover roughly 100 grains due to the randomness of the grain sizes and shapes [57]. The other considerable challenge is the write-process must be synchronized carefully with the locations of the medium islands i.e. each single-domain magnetic island should store one bit.

In HAMR the significant component is the recording head [8]. The writing area is mag-

Figure 1.5: Schematic View of the Bit-Patterned Media [6]

Figure 1.6: Schematic View of HAMR Technology [7]

netized by a laser embedded in the write head as shown in Figure 1.6, which heats the medium then cooling it back to an ambient temperature to get the required magnetization. Figure 1.7 illustrates schematically the three future techniques options.

### **1.8 Shingled Writing Technology**

The current magnetic recording technology, PMR, has reached a limitation which is imposed by superparamagnetic effect, the media trilemma [56]. While the theoretical limit of this technology is 1 Tbit/in<sup>2</sup>, the current drives capacity is 400 Gbit/in<sup>2</sup> [56] [58]. However, the highest demonstrated areal density that could be achieved with continuous perpendicular medium is 612 Gbit/in<sup>2</sup> [8].

As a result, demands for a new recording technology have arisen to cover the 30-50% annual growth [50][56] [8] of the data density. SMR is the more powerful candidate among different technologies to replace the conventional magnetic recording. SMR is easy to implement as it can be built on the existing technology so that there is no need to change the media of PMR method. However, a few changes are required on the write head because the writing needs much stronger magnetic field compared to the reading process. The fundamental concept of SMR is overlapping of tracks, like shingling (laying) tiles on a roof as shown in Figure 1.8. The stronger and asymmetric magnetic field offered by the write head of shingled system would help making the overlapping possible. The shingled-writing is like overlapping of newly written tracks with preceding tracks leaving only a small strip of the previous track as a record of the original data. Placing tracks closer together would allow more data to be recorded. This small strip of the written track could be read by the current GMR head. Nevertheless, there are still some disadvantages in this technology such as the writing should be done sequentially. But this technology still offers random access readout where the readback process is unaffected [56][8]. In addition, a considerable disadvantage which is "update-in-place" is no longer possible [9]. In other words, rewriting a single track or a portion of it would require recovering the information written on the subsequent adjacent tracks.

Another technology has been proposed to extend the existing heads and media to higher

Figure 1.8: Shingled Magnetic Recording Technique Process [9]

storage density, namely Two-Dimensional Magnetic Recording (TDMR). TDMR combines two techniques: SMR and Two-Dimensional (2-D) readback which requires a powerful signal processing. However, TDMR could be used alone or in conjunction with SMR [8].

# 1.9 Aim and Objectives

Many areas are recognized as the key components that play a significant role in disk drive capacity such as recording technique, materials, manufacturing and signal processing tools. The improvements in head, media, mechanical designs and advances in signal processing techniques could achieve high recording density [59]. Also, using magnetic recording system that record each bit of data on very few magnetic grains together with signal processing system that have the capability to recover the data reliably would achieve the highest areal densities [50]. Although the current disk drives are approaching 400 Gb/in<sup>2</sup>, Wood, *et al.* [50] predicated that the limit of the conventional magnetic recording is around 1 Tbit/in<sup>2</sup>.

The main obstacle of the growth of HDD capacity is the thermal stability (superparamagnetic effect) of the magnetic grains that comprise the magnetic material [50]. The superparamagnetic effect causes erasing of the recorded data after a short period of time [10]. Increasing the storage density requires shrinking the grains size which in turn decreases the magnetic anisotropy energy of the grains (*KuV*, where *Ku* is the anisotropy of the grain and *V* is its volume) to become less than  $K_BT$  (where  $K_B$  is Boltzmann's constant and *T* is the absolute temperature) then the magnetization will be switched [45][60].

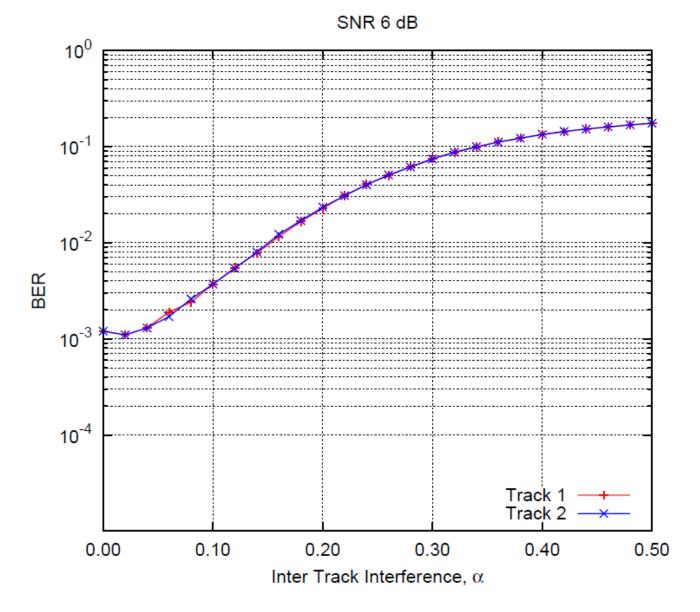

In addition, the other obstacle that prevents data storage growth is the ITI. The rapid growth of digital data requires higher storage density which in turn requires either reducing track widths, or reducing the space between tracks, or a combination of both. Perpendicular recording technology stores the data in concentric circular tracks which are reasonably isolated with guard bands [61]. Shingled systems can increase the storage capacity by reducing those guard bands. In shingled magnetic recording, the data can be written sequentially using a wide write head with tracks squeezing (no guard bands)[62] [63]. However, this squeezing causes tracks to overlap one another which in turn increases ITI that will lead to performance degradation.

The aim of the research is investigating the ITI and reducing the complexity of the shingled system decoder. To achieve this aim, the work is carried out by the following objectives:

- Investigation and implementation of PRML channel model as a platform in order to accomplish the data recovery process where this process indicates the performance of the magnetic recording system. PRML channel implementation is developed as follows:

- Designing and simulation of PMR channel.

- Implementation of Partial Response (PR) equaliser to reshape the PMR channel response into a specific target response.

- Investigation and implementation of VA as an optimal sequence decoder to recover the written data. Then this algorithm is modified to reduce BER which would improve the performance of the PRML channel.

- Investigation and implementation of Maximum A Posteriori (MAP) algorithm as an optimum bit based decoder. This algorithm is also modified for the same channel and a comparison is made between the two algorithms.

- 2. Investigation of shingled system as an alternative technique of perpendicular recording method to increase the disk density. Shingled technology can be built on the same media of perpendicular recording with few changes to the write head.

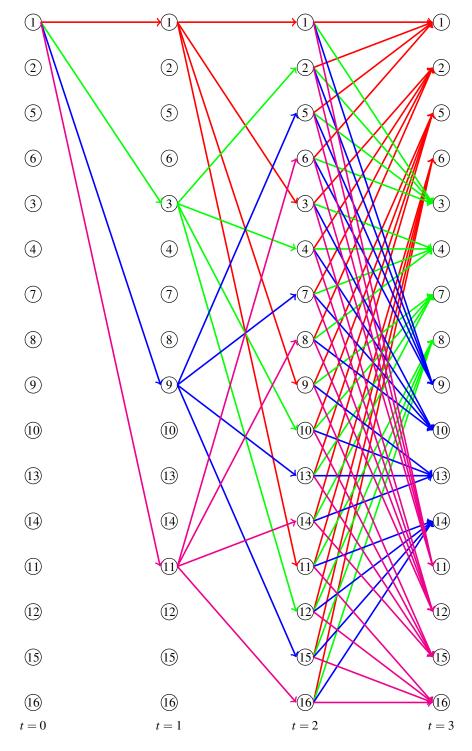

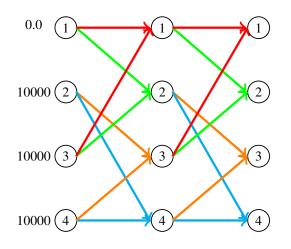

- 3. Implementation of shingled system by extending the PRML system model of Step 1 into a two-track model to include the ITI of the adjacent track. Implementation of the two-track system model requires extension of the channel trellis of one-track system model. Consequently, a complicated 16-state trellis with four incoming paths and four outgoing paths at each state would be constructed which will make the complexity of the new system decoder trellis very high. Therefore, an intensive work is required in order to reduce the complexity of this trellis.

- 4. Implementation of one-track system model in hardware to measure its complexity.

# 1.10 Contributions to Knowledge

This thesis covered many aspects of decoder design for perpendicular recording and shingledwriting systems. The original contributions to the knowledge of the author are listed below:

- 1. Two decoding techniques used for perpendicular magnetic recording which are the optimal sequence decoder (VA) and the optimal bit-based decoder (MAP). The algorithms are modified based on the pdfs histogram of the output samples of the ideal channel (target). The derivation of maximum likelihood sequence for ML decoder is given considering the pdfs distribution of the ideal channel samples. From the derivation, it is found that the new maximum likelihood sequence involves additional term which will require adding one sum in the path metric computations of the channel trellis. VA is modified by adding the new term to the path metric computations. MAP is modified by adding the new term to the transition probabilities computations.

- 2. Investigation of the ITI in shingled magnetic recording systems requires construction two-track one head system model. The ITI can be considered as either a noise added to the AWGN of the system or a signal which would increase the SNR.

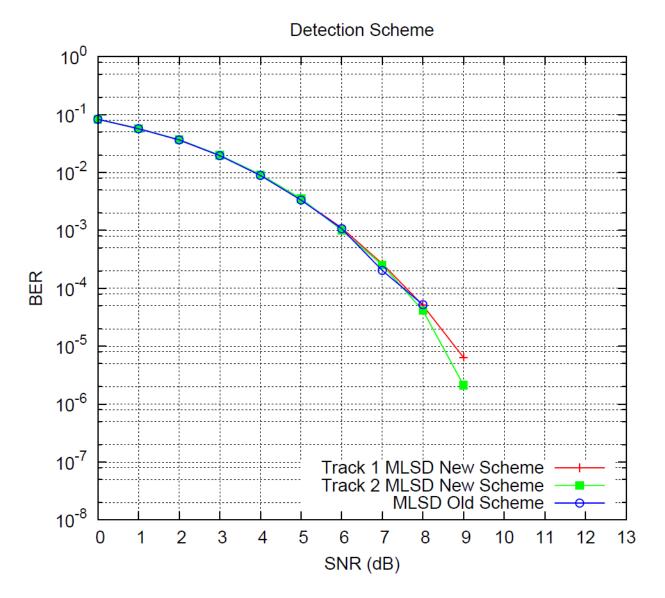

If the ITI is treated as a noise, the BER exceeds  $10^{-1}$  at 6 dB SNR. However, if the system has no ITI, the BER is almost  $10^{-3}$  for the same SNR.

If the equaliser views the ITI as a signal, then 16-state trellis with four outgoing paths from every state and four incoming paths to every trellis state is required to accomplish all the possibilities of the channel. MLSD is applied to find the most likely path sequence in the trellis of the shingled system. Consequently, different decoding techniques have been found. The decoding techniques show different performances with different complexities. The conventional technique (without simplification) shows an optimal performance with high complexity. However, the one common factor technique has the closest performance to the optimal one where the difference between the two performances becomes larger at higher amount of ITI (more than 30%).

In terms of complexity, the one common factor approximation has the lower complexity. However, the complexity could be reduced further if some terms of the approximation are completed off-line. Consequently, the complexity is reduced more than three times compared with the complexity of the conventional technique. The simulation results showed that a trade-off can be made between the BER and the complexity.

The author has presented this contribution at:

- Intermag 2012 Conference.

- Joint MMM/Intermag 2013 Conference.

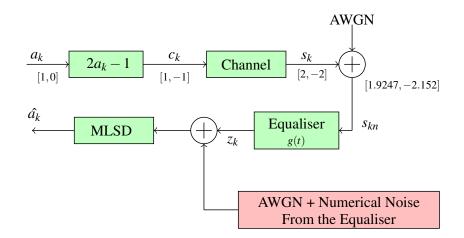

3. In order to measure the complexity of one-track one head system model, PRML channel is verified in hardware using Altera Field-Programmable Gate Array (FPGA) development board. PRML system is divided into four components for implementation purpose in Simulink/DSP Builder softwares which are: PMR channel, PR equaliser, ideal channel (target) and VA components. These components have been verified in hardware expect VA architecture. Consequently, a conclusion has been made which is Simulink/DSP Builder softwares are ideal for low complexity designs. However for complex designs, HDL code is the eligible solution.

The author has published this work at 3rd International Symposium on Advanced Magnetic Materials and Applications 2013.

# 1.11 Thesis Structure

This thesis is organized in the following way:

Chapter 2 presents a general knowledge of PRML system in magnetic recording systems which include equalisation and detection algorithms. The aim of this chapter is to provide a background information about signal processing which will help simulating the PRML system to perform the data recovery process.

Chapter 3 discusses PRML system implementation to evaluate the system performance in terms of BER graphs. Also in this chapter, two optimum detection algorithms will be modified in order to improve the PRML system performance.

Chapter 4 investigates SMR system and discusses adding ITI amount into the one-track model that described in Chapter 2 and then extend it into two-track system. New trellis, 16-state, with four incoming paths and four outgoing paths at each state is constructed. Six novel decoding techniques have been found with very high complexity. Intensive work has been done in order measure and then reduce their complexities. One technique (one common factor) had a better performance which was very close to the optimal one. The complexity of this technique has been measured and it is found that some computations can be completed off-line while the others can be completed on-line. Off-line means while the equaliser output sequence is being equalised, the computations that do not depend on the equaliser output sequence can be computed. Consequently, the complexity of one common factor method has been reduced further. The simulation results showed that a trade-off can be made between the BER and the complexity.

Chapter 5 provides an introduction to the simulation softwares that will be used to implement PRML system in hardware. Those softwares are Simulink of Math-Works, ModelSim and Altera Quartus II softwares. Also, it explains some features of STM32F4 High-Performance Discovery board and Altera DE1 development and education board. The two boards will be used to verify the hardware design of PR equaliser model.

Chapter 6 discusses many hardware architectures of PRML system including PMR

channel, PR equaliser without and with AWGN, ideal channel (target) and 4-state trellis structure. Those architectures are implemented in Simulink/DSP Builder softwares and then in Quartus II. A conclusion has been made which is designing using Simulink/DSP Builder softwares is ideal for the designs with low complexity however for the complicated designs the alternative solution is using HDL.

Chapter 7 the work presented in this thesis is concluded. Where this chapter is summarised the main contributions of this work and gives some suggestions as a future work to improve and develop the research in this area.

# **Chapter 2**

# **Overview of PRML Read Systems**

# 2.1 Introduction

Generally, PRML systems have been used in communication channels since 1960s and then in magnetic recording channels in 1970 as a technique to combat the ISI effect. In the PRML system, Viterbi detector which is an ML detector, is applied to convert the received sequence into a corresponding sequence of detected bits. MAP algorithm is also applied to the data storage channels as an optimum detector based on bit detection rather than sequence detection.

The most important part of any data storage system is the process of recovering the written data that is transmitted through the magnetic recording systems. Therefore, this chapter will present in detail the process of recovering and will review every part of the PRML system which includes the two detection algorithms.

# 2.2 Data Storage Channel Model

The similarity between digital communication system and data storage system is in the main goal, namely the reliability in receiving the transmitted information (data). In both systems, information is transmitted through noisy channels and then recovered by using efficient means. The difference between the two scenarios is that the information in communication systems is transported from one location to another at the same time. Whereas in the data storage system, transmitting the information occurs from one time to another at

Figure 2.1: Data Storage System Block Diagram [10][11]

same location [51][64].

Figure 2.1 depicts data storage system model. The information bits are encoded and protected by error correction codes. Modulation coding is applied to control the minimum and maximum distances between consecutive magnetic transitions. In other words, using modulation coding would help eliminate the arbitrary sequence of user data from a recorded stream. The minimum distance constraint is used to avoid media noise and non-linearity associated with the crowded magnetic transitions. The maximum distance constraint is applied to ensure the existence of the signal at readback. The constraints of RLL(d,k) code are the most known constraints for data storage channel where *d* is the distance that separates 1's and *k* for 0's. The modulated data sequence is converted into a rectangular current waveform and then stored in the medium as a magnetization form. The read waveform is a linear superposition of shifted transition responses where every single written transition is a transition response [10].

#### 2.2.1 Longitudinal Magnetic Recording Channel Model

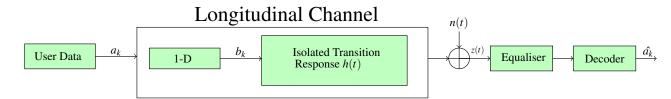

Figure 2.2 shows the simulated LMR channel model. The (1-D) block is inherent with the longitudinal magnetic channel due to the differentiation property in the readback process [65] produced by the magnetic read head. Magnetic recording channel can be considered

Figure 2.2: Simulated Longitudinal Recording Channel Model

as a linear time-invariant system [66] [54]. As a result, the read waveform of longitudinal channel is [10]

$$z(t) = \sum_{k} (a_k - a_{k-1})h(t - kT) + n(t)$$

(2.1)

Where  $a_k$  is the user data which is a sequence of 1's and 0's,  $b_k = a_k - a_{k-1}$ , h(t) is the isolated transition response, T is the bit interval and n(t) is AWGN due to the read head and electronics [10].

In LMR, the MR read head generates an output voltage from a magnetic transition. Consequently, each magnetic transition produces an opposite output voltage of the previous transition and zero output voltage for no magnetic transitions regions. Therefore LMR readback signal is a dc-free signal. Contrary to PMR, the output voltage will be obtained from the regions of constant magnetic polarity while at the magnetic transition region the MR read head constructs zero output voltage. Thus, PMR readback signal is a non-zero dc-response [67].

The reading head impulse response, h(t), is governed with the shape of magnetization and it is modeled as a Lorentzian pulse [10]. As it was mentioned in Chapter 1, the writing process is accomplished by the write head. It records the data on the disk surface by magnetizing the storage media, that moves below the head, into two opposite directions representing either bit 0 or bit 1. Subsequently, the read head reads the recorded data by sensing the change of the magnetic field arising from the disk. The read out signal could be characterized by the transition responses h(t) and (-h(t)). Here, h(t) indicates a positive transition from bit 0 to bit 1 and (-h(t)) means the transition is from bit 1 to bit 0.

The Lorentzian pulse of the longitudinal recording transition response is expressed as [10]

$$h(t) = \left(\sqrt{\frac{4E_t}{\pi P W_{50}}}\right) \left(\frac{1}{1 + (2t/P W_{50})^2}\right)$$

(2.2)

Where  $E_t = \int |h(t)|^2 dt$  is the amount of energy in the transition response and  $PW_{50}$  is the width of Lorentzian pulse, h(t), at half of its peak value.  $PW_{50}$  is related to the head and the media and not related to the operating normalized density therefore,  $PW_{50}$  is fixed for a fixed head and media combination [10]. The term  $\sqrt{\frac{4E_t}{\pi PW_{50}}}$  can be set to 1 as a normalization factor. Thus, transition response could be reduced to:

$$h(t) = \frac{1}{1 + (2t/PW_{50})^2}$$

(2.3)

The response of two adjacent transitions, dibit, can be expressed as [22][54]

$$d(t) = \frac{1}{1 + (\frac{2t}{PW_{50}})^2} - \frac{1}{1 + (\frac{2(t-1)}{PW_{50}})^2}$$

(2.4)

The longitudinal channel has been simulated using MATLAB written by the author in order to find the impulse response of this channel as follows [10]

$$x_i = \frac{1}{1 + (2i/(D_s \cdot osr))^2}$$

(2.5)

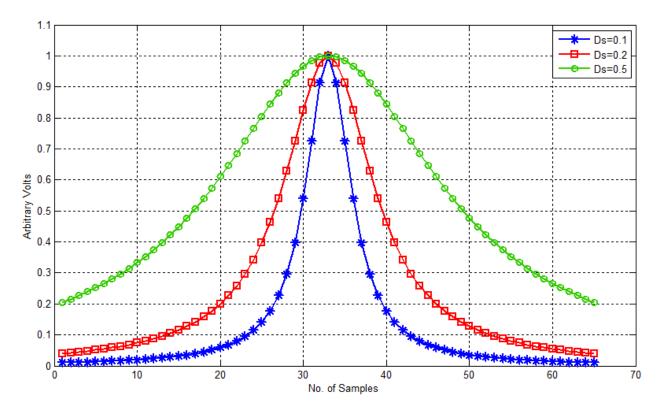

Where  $i = 0, 1, 2, ..., x_i$  is the i-th sample in the oversampling domain,  $D_s = 0.1$  and osr =65.  $D_s = PW_{50}/T$  is the normalised density where  $PW_{50}$  is normalised to the bit period, *T*, and osr is the number of samples.

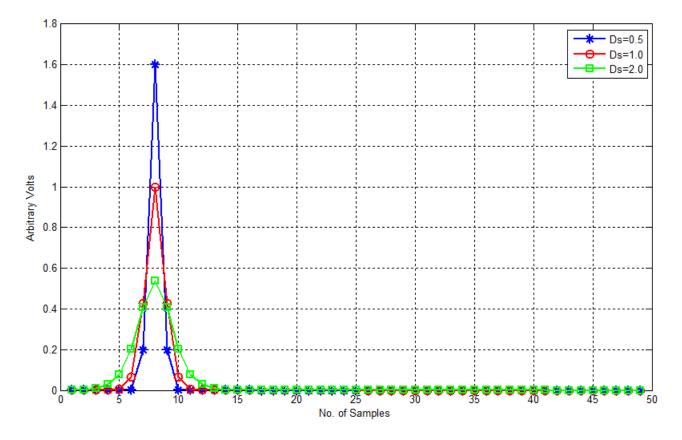

Increasing the storage density requires increasing the recorded bits per the interval w, w =

Figure 2.3: Sampled Transition Response of Longitudinal Recording at Different Linear Densities

$PW_{50}$ , which in turn causes the overlapping and then more ISI as shown in Figure 2.3. The communication channels, including data storage channels, are characterized as bandlimited filters. Accordingly, such channels are described by their frequency response H(f), which is [10]

$$H(f) = A(f)e^{j\theta(f)}$$

(2.6)

Where A(f) is the amplitude response and  $\theta(f)$  is the phase response. Sometimes group delay or envelope delay is used instead of phase response, that is [10]

$$D(f) = -\frac{1}{2\pi} \frac{d\theta(f)}{df}$$

(2.7)

Figure 2.4: Simulated Perpendicular Recording Channel Model

The frequency response of Equation (2.4) is [22][54]

$$H(w) = (1 - e^{-jwT}) \frac{PW_{50}}{2} \pi e^{-w \frac{PW_{50}}{2}}$$

(2.8)

Where w is the frequency term and T is the sampling period.

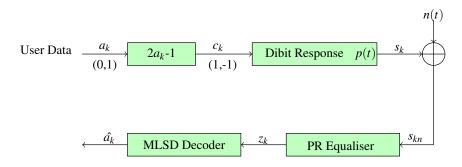

# 2.2.2 Perpendicular Magnetic Recording Channel Model

Figure 2.4 depicts the simulated PMR system model. The implementation of the PMR channel in MATLAB will be discussed in Chapter 3. The readback signal can be described by [10]

$$z(t) = \sum_{k} c_{k} p(t - kT) + n(t)$$

(2.9)

Where, p(t - kT) = h(t - kT) - h(t - (k - 1)T). For each single written transition, the transition response is modelled as [10]

$$h(t) = V_p.erf\left((2\sqrt{ln2})\frac{t}{PW_{50}}\right)$$

(2.10)

where erf(x) is the error function, stated as:

$$erf(t) = \frac{2}{\sqrt{\pi}} \int_0^t e^{-x^2} dx$$

(2.11)

$V_p$  is the peak voltage value of the transition response and  $PW_{50}$  is the time taken for h(t) to go from  $-V_p/2$  to  $+V_p/2$ .

For simulation purposes, the transition response can be approximated by a hyperbolic tangent function, *tanh* [52]

$$h(t) = V_p \tanh\left(\ln(3)\frac{t}{D_s}\right)$$

(2.12)

Figure 2.5 shows the sampled transition response for perpendicular recording. The dibit response, p(t), is:

$$p(t) = h(t) - h(t - T)$$

(2.13)

Increasing the normalised density would decrease the amplitude of the dibit response which in turn reduces the power of the readback signal [10] as shown in Figure 2.6.

# 2.3 PRML Method

Peak detection and RLL coding have been used for decades as a reliable technique with 100 000 bits/mm<sup>2</sup> storage density [59]. The concept of the peak detector, symbol-by-symbol detector, is based on detecting the isolated peak of each transition written on the magnetic media. The detector works effectively with low recording density where the pulses are obviously separated and each transition written results in a relatively isolated voltage peak [10][12][42]. At high recording density, the problem of ISI arises and the pulses overlap each other which would effect the capability of the peak detector to recover the recorded data reliably. Consequently, high density storage requires more sophisticated detection methods in order to mitigate the ISI effects. Therefore, it was necessary to find another

Figure 2.5: Sampled Transition Response of Perpendicular Magnetic Recording System

technique that would overcome the peak detector degradation when the amount of ISI is considerably large. For that reason, the PRML method was proposed and then became the dominant detection scheme in commercial HDDs.

PRML method is used as a signal processing technique for high density longitudinal and perpendicular recording systems. The digital cassette tape recording device was the first storage product which used PRML and was introduced by Ampex in 1984. It was reported in [68] that, using the PRML method on an experimental disc recording system achieved 56 Mb/in<sup>2</sup>. The first HDD -IBM 0681 was shipped in 1990, used PRML technique [69]. At the beginning of 1990's, most of the drives industry had been applying the peak detection method with an exception of a few IBM drives using PRML technique and later on the entire industry was replaced with the PRML method [10].

Figure 2.6: Sampled Dibit Response of Perpendicular Recording at Different Linear Densities

Moreover, in 1970 the theoretical studies done by Kobayashi and Tang at IBM suggested that the maximum likelihood sampling detector and PR equalisation was possible to apply to the magnetic recording channels [65]. Also, Cideciyan, *et al* in [59] have showed that applying PR signalling in combination with Maximum-Likelihood Sequence Detection (MLSD) allows further progress in increasing the storage density and recovering the recorded data reliably over the conventional technique (RLL coding and peak detection method). This work [59] also proved that the PRML technique is suitable for digital magnetic recording applications.

The frequency responses of magnetic recording systems that use inductive or MR head (for

longitudinal recording) have similar characteristics, both have a null at DC. Also, the frequency responses decrease exponentially with frequency at high frequencies. Therefore, magnetic recording channels are considered as band-pass channels [59]. A question arises if the sampling frequency in the PRML system is high enough to recover the recorded transition. The Nyquist sampling theorem, states a principle of analog signals digitization which is the sampling frequency should be at least twice the highest frequency contained in the signal. For instance, if a channel bandwidth is *WHz* then the maximum binary transmission rate with zero ISI is 1/T = 2W symbols/sec [10]. Therefore, sampling once per channel period *T* is appropriate only if the spectrum of the analog readback signal is concentrated below the frequency  $f_{max} = 1/2T$  [12].

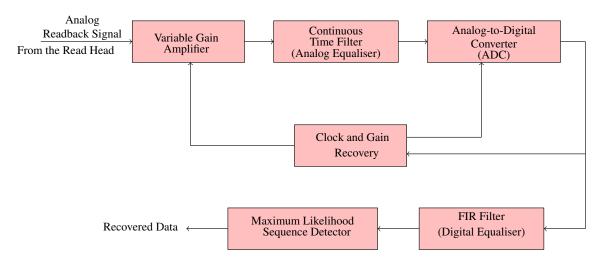

Figure 2.7 shows the block diagram of a typical PRML channel. Variable-Gain Amplifier (VGA), analog equaliser, Analog-to-Digital Converter (ADC) and digital equaliser blocks transform the readback signal into a partial response signal. The magnetic read head produces an analog readback signal, with different levels of amplification which in turn leads to get different peaks of the readback signal. VGA compensates that variation in the signal peaks and amplifies them to have a certain and constant level of amplification. A clock signal is used to sample the analog waveform to obtain the discrete samples. The clock and gain recovery blocks provide a control signal to the VGA. The analog equaliser (Continuous Time Filter, CTF) block which has a specified frequency response and specific bandwidth, would determine the spectral components of the readback signal by filtering out the unwanted components that are beyond the specified bandwidth. The reason for that is to satisfy the Nyquist theorem. The analog equaliser performs another function which is modifying the frequency response of the channel. Modification is necessary to adjust the shape of the readback signal from the magnetic head. Then the analog equaliser output signal is sampled with the ADC and the sampling process is initiated by a clock signal. The

Figure 2.7: Block Diagram of Typical PRML Channel [12]

rate of the clock signal is one sample per channel bit period where this rate is adjusted by the clock recovery loop. Now, the signal at the ADC output is a stream of digital samples or discrete-time data. The possibilities of ADC are between 0 and  $2^n - 1$ , where *n* is the number of bits in ADC. Another digital filter is applied to remove the unwanted samples which in turn improve the quality of analog equalisation that performed by the CTF [12]. The purpose of this process is to reshape the partial response channel into a predefined response and then apply it to the ML detector to recover the original data [16]. Depending on the desired time and frequency response of the signal, different classes of PR targets for equalisation exist and this will be explained in the following section.

#### 2.3.1 Partial Response Equalisation

Instead of eliminating the ISI, PR equalisation controls the amount of ISI that enters the detector [10]. The equalisation process is regarded as a "partial response" equalisation rather than "full response" equalisation because the later means removing the whole ISI [66]. The basic idea of the PR equaliser is leaving a controlled amount of ISI to the detector to combat [42]. This amount is allowed in order to match the PR signal spectrum to the

recording channel characteristics [59]. However, Kobayashi was the first one who noted applying the PR signals in magnetic recording systems in order to increase the storage density [70]. The magnetic recording channel could be transformed into a PR channel as long as it is satisfied two fundamental features; the superposition of voltage pulses from adjacent transitions is linear and the shape of the readback signal from an isolated transition is exactly known and determined [12]. The frequency spectrum of a linear magnetic channel is usually defined as the Fourier transform of its pulse response [12][45]. An experimental spectrum has been obtained from a channel which had a random pattern of transmitted data. The pattern had an equal number of positive and negative transitions therefore no spectrum content at zero frequency (DC content is zero) but the readback signal has high frequency components. Since that pattern contains all spectral components with frequencies of 1/2nT, where n = 1, 2, 3, ..., this spectrum should have the Fourier transform of the single (isolated) pulse [12]. Also, the spectrum is concentrated below 1/2T, though the tail of it was outside the 1/2T range. According to that the PRML channel is appropriate for magnetic recording systems as long as the frequency spectrum can be readily equalised by CTF with a cutoff frequency of 1/2T [12][45].

Kretzmer defined the classes of PR in [71] where the first widely used PR channel is Class IV Partial Response (PR4) channel [12]. The performance of PR4 is matched to the spectrum of a typical readback pulse over a range of recording densities [70]. In PR4 system, each voltage has two samples i.e. if a transition of magnetization occurs it gives a "1" at the transition location and another sample at the next sample period. This can be described by the " spreading" operator (1+D). Thus, the PR4 can be described as  $(1-D)(1+D) = 1 - D^2$  polynomial. Table 2.1 summarizes the PR channels where in 1990's, the PR4 channel became the darling of the magnetic data storage industry [12]. However, different PR schemes can be described by the following polynomial [71]:

| Name | Polynomial                    | Impulse Response Samples |

|------|-------------------------------|--------------------------|

| PR1  | 1+D                           | 0 1 1 0                  |

| PR2  | $(1+D)^2 = 1+2D+D^2$          | 0 1 2 1 0                |

| PR3  | $(1+D)(2-D)=2+D-D^2$          | 0 2 1 -1 0               |

| PR4  | $(1+D)(1-D)=1-D^2$            | 010-10                   |

| PR5  | $-(1+D)^2(1-D)^2=-1+2D^2-D^4$ | 0 -1 0 2 0 -1 0          |

Table 2.1: Partial-Response Channels

$$F(D) = (1-D)(1+D)^n, n = 1, 2, 3, \dots$$

(2.14)